Agilent Technologies HDMP-3001 User Manual

Page 117

117

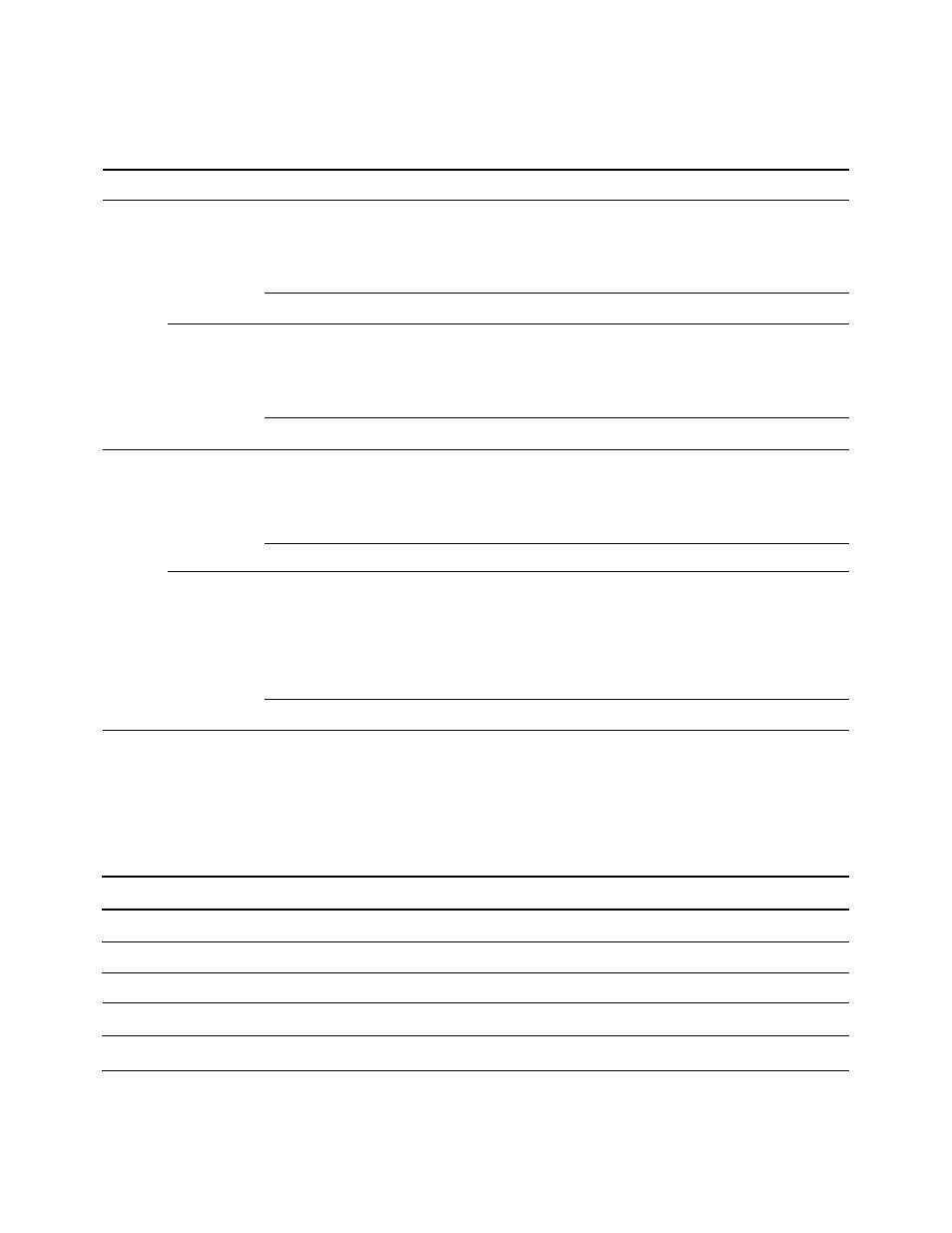

Table 31. MII signal clocking

Mode

Direction

Pin name

In/Out

Note

PHY

TX

P_TXD[3:0]/M_RXD[3:0],

In

Clocked in by

P_TX_EN/M_RX_DV,

P_TX_CLK/M_RX_CLK

P_TX_ER/M_RX_ER

P_TX_CLK/M_RX_CLK

Out

RX

P_RXD[3:0]/M_TXD[3:0],

Out

Clocked out by MII_RX.

P_RX_DV/M_TX_EN,

P_RX_ER/M_TX_ER

P_RX_CLK/M_TX_CLK

Out

Inverted version of MII_RX.

MAC

TX

P_RXD[3:0]/M_TXD[3:0],

Out

Clocked out by

P_RX_DV/M_TX_EN,

P_RX_CLK/M_TX_CLK.

P_RX_ER/M_TX_ER

Max 25 ns round-trip delay.

P_RX_CLK/M_TX_CLK

In

RX

P_TXD[3:0]/M_RXD[3:0],

In

Clocked in by

P_TX_EN/M_RX_DV,

P_TX_CLK/M_RX_CLK

P_TX_ER/M_RX_ER

P_TX_CLK/M_RX_CLK

P_TX_CLK/M_RX_CLK

In

Label

Parameter

Min

Max

Units

MDC

MDC frequency

-

2.5

MHz

t

STASU

Setup MDIO to MDC high, STA driving MDIO

10

ns

t

STAHD

Hold MDIO from MDC high, STA driving MDIO

10

ns

t

PHYVL

MDC high to MDIO valid, HDMP-3001 driving MDIO

300

ns

t

MINHL

MDC minimum high and low time (duty cycle)

160

-

ns

8.12 MDIO Port Timing

The MDIO port timing of HDMP-3001 conforms to the IEEE 802.3 specification, clause 22.