Agilent Technologies HDMP-3001 User Manual

Page 95

95

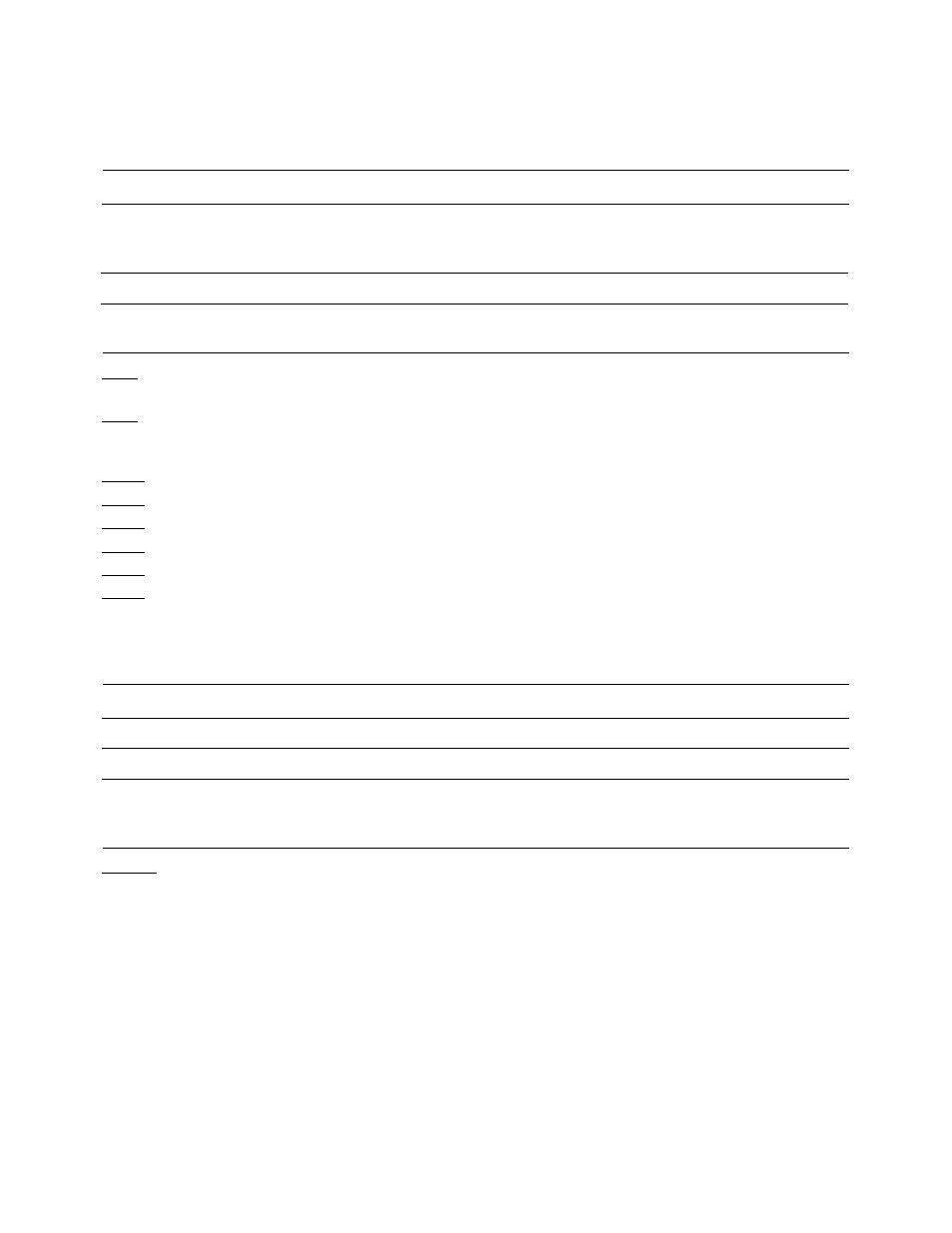

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name

RX_EXT_

RX_TYPE_

RX_EHEC

RX_THEC

RX_TYPE

RX_SPARE

RX_DP_

RX_SP_

HDR_REM HDR_REM

_CHECK_

_CHECK_

CHECK_

_CHECK

CHECK_

CHECK_

_INH

_INH

INH

INH

INH

_INH

INH

INH

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Value

0

0

0

0

0

0

0

0

reset

ADDR = 0x1CE: GFP Mode

Bit 7:

RX_EXT_HDR_REM_INH

is set for GFP null headers. When set, the GFP Payload begins right

after the tHEC field. When cleared, the four bytes after the tHEC are the Linear Extended Header.

Bit 6:

RX_TYPE_HDR_REM_INH

is set to inhibit the removal of the received Type Header for test

purposes. When set, this field is prepended to the MAC Payload. When cleared, this field is not

forwarded through the MII interface.

Bits 5:

RX_EHEC_CHECK_INH

is set to inhibit the checking of the received eHEC field.

Bits 4:

RX_THEC_CHECK_INH

is set to inhibit the checking of the received tHEC field.

Bits 3:

RX_TYPE_CHECK_INH

is set to inhibit the checking of the received Type field.

Bits 2:

RX_SPARE_CHECK_INH

is set to inhibit the checking of the received Spare field.

Bits 1:

RX_DP_CHECK_INH

is set to inhibit the checking of the received DP field.

Bits 0:

RX_SP_CHECK_INH

is set to inhibit the checking of the received SP field.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Bit name RX_SPARE[7:0]

R/W

R/W

Value

0x00

after

reset

ADDR = 0x1CF: Receive Spare Field Byte

Bits 7-0: RX_SPARE[7:0] specifies the expected Spare Field when in GFP mode. If

RX_SPARE_CHECK_INH is not set, frames with a non-matching Spare Field are discarded and the

Form/Dest Error counter is incremented.