Rainbow Electronics DS2153Q User Manual

Page 34

DS2153Q

022697 34/48

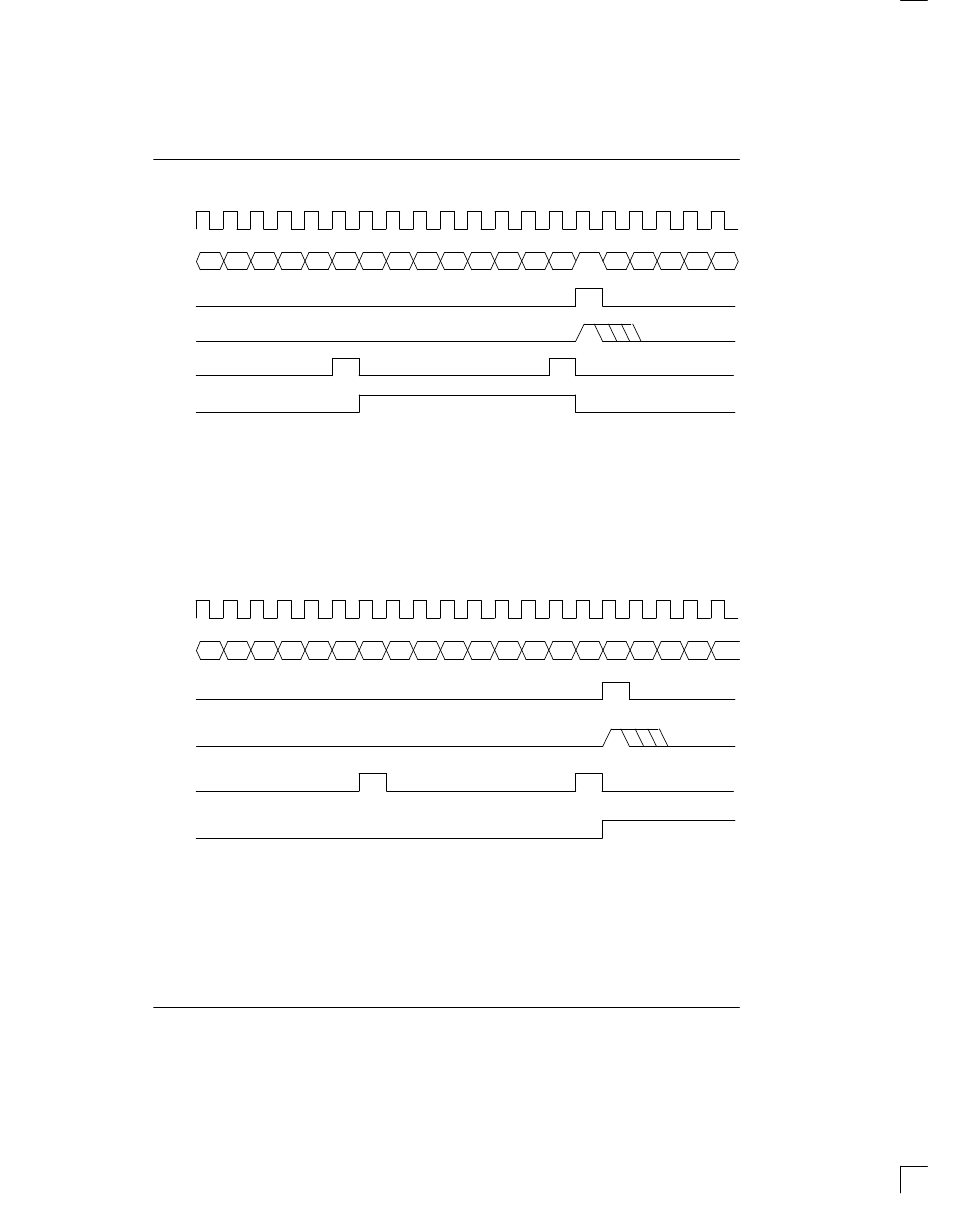

1.544 MHz BOUNDARY TIMING WITH ELASTIC STORE(S) ENABLED Figure 13–3

SYSCLK

RSER

1

,

RSYNC

2

RSYNC

3

RCHCLK

RCHBLK

4

CHANNEL 24/32

CHANNEL 1/2

CHANNEL 23/31

LSB MSB

LSB

MSB

F

TSER

NOTES:

1. Data from the E1 channels 1, 5, 9, 13, 17, 21, 25, and 29 is dropped (channel 2 from the E1 link is mapped to

channel 1 of the T1 link, etc.) and the F–bit position is added (forced to one).

2. RSYNC is in the output mode (RCR1.5=0).

3. RSYNC is in the input mode (RCR1.5=1).

4. RCHBLK is programmed to block channel 24.

2.048 MHz BOUNDARY TIMING WITH ELASTIC STORE(S) ENABLED Figure 13–4

SYSCLK

RSER,

RSYNC

1

RSYNC

2

RCHCLK

RCHBLK

3

CHANNEL 32

CHANNEL 1

CHANNEL 31

LSB MSB

LSB

TSER

NOTES:

1. RSYNC is in the output mode (RCR1.5=0).

2. RSYNC is in the input mode (RCR1.5=1).

3. RCHBLK is programmed to block channel 1.

- MAX12005 (14 pages)

- MAX7058 (14 pages)

- MAX9995 (13 pages)

- MAX7034 (13 pages)

- MAX7033 (16 pages)

- MAX9476 (8 pages)

- MAX9486 (8 pages)

- MAX14821 (29 pages)

- MAX9489 (11 pages)

- MAX9491 (11 pages)

- DS2130Q (22 pages)

- DS21458 (270 pages)

- DS3131 (174 pages)

- DS26502 (125 pages)

- DS26503 (123 pages)

- DS2186 (11 pages)

- DS1842A (6 pages)

- DS3134 (203 pages)

- DS1876 (69 pages)

- DS1874 (88 pages)

- DS31256 (181 pages)

- DS2141A (35 pages)

- DS3184 (13 pages)

- DS2154 (69 pages)

- DS26504 (128 pages)

- DS3164 (12 pages)

- DS1852 (25 pages)

- DS2181A (32 pages)

- DS2151Q (46 pages)

- DS1843 (8 pages)

- DS2165Q (17 pages)

- DS3170 (233 pages)

- DS2180A (36 pages)

- DS2172 (20 pages)

- DS2152 (79 pages)

- DS1841 (16 pages)

- DS2182A (22 pages)

- DS2143Q (40 pages)

- DS2132A_Q (17 pages)

- DS1862 (42 pages)

- DS26519 (310 pages)

- DS2188 (11 pages)

- DS1875 (92 pages)

- DS33M33 (20 pages)