Access without the management interface, Table 8-13 – Xilinx LOGICORE UG144 User Manual

Page 90

90

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 8: Configuration and Status

R

-- DISCONTINUED PRODUCT --

Access without the Management Interface

If the optional management interface is omitted from the core, all of the relevant

configuration settings described in

through

are brought out of the core

as signals. These signals are bundled into the configuration_vector[67:0] signal as

described in

These signals may permanently set by connecting to logic 0 or 1, or may be changed by the

user application at any time; however, with the exception of the reset and the flow control

configuration signals, any changes do not take effect until the current frame has completed

transmission or reception.

The Clock heading in

denotes which clock domain the configuration signal is

registered into before use by the core. It is not necessary to drive the signal from this clock

domain.

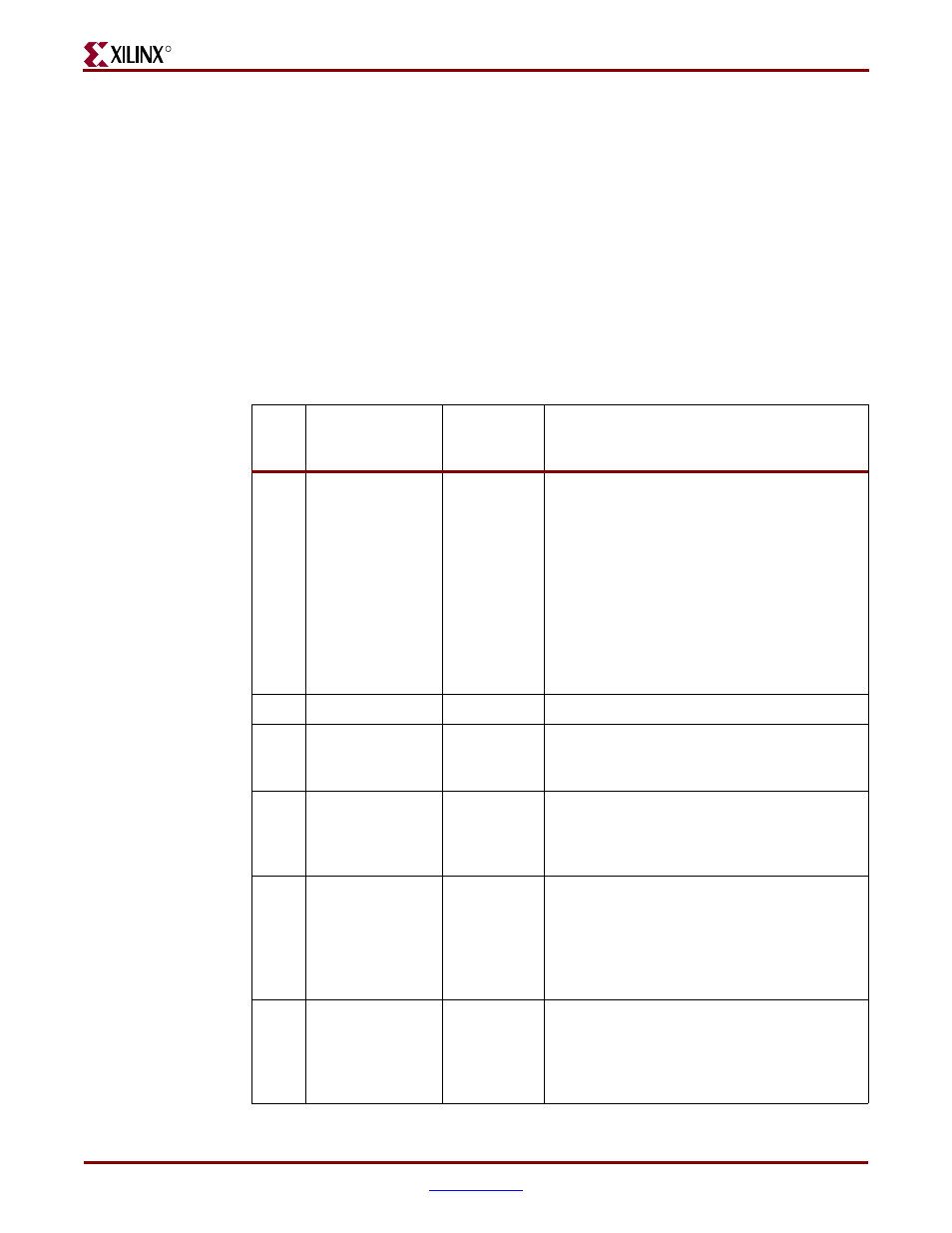

Table 8-13:

Configuration Vector Bit Definition

Bit(s)

Configuration

Register cross

reference

Clock

Description

47:0

“Receiver

Configuration

Word 0”

bits 31-0

and

bits 15-0

gmii_rx_clk

Pause frame MAC Source Address[47:0]

This address is used by the GEMAC core to

match against the destination address of any

incoming flow control frames, and as the

source address for any outbound flow control

frames.

The address is ordered such that the first byte

transmitted or received is the least significant

byte in the register; for example, a MAC

address of AA-BB-CC-DD-EE-FF will be

stored in bite [47:0] as 0xFFEEDDCCBBAA.

48

n/a

n/a

This input is unused.

49

“Receiver

Configuration

Word 1”

bit 27

gmii_rx_clk

Receiver VLAN Enable

When this bit is set to

'1,’ VLAN tagged frames are accepted by the

receiver.

50

“Receiver

Configuration

Word 1”

bit 28

gmii_rx_clk

Receiver Enable

If set to '1,’ the receiver

block is operational. If set to '0,’ the block

ignores activity on the physical interface RX

port.

51

“Receiver

Configuration

Word 1”

bit 29

gmii_rx_clk

Receiver In-band FCS Enable

When this bit

is ‘1,’ the MAC receiver will pass the FCS

field up to the client. When it is ‘0,’ the MAC

receiver will not pass the FCS field. In both

cases, the FCS field will be verified on the

frame.

52

“Receiver

Configuration

Word 1”

bit 30

gmii_rx_clk

Receiver Jumbo Frame Enable

When this bit

is ‘0,’ the receiver will not pass frames longer

than the maximum legal frame size specified

in IEEE 802.3-2005. At ‘1,’ the receiver will not

have an upper limit on frame size.