Integration to provide 1000base-x pcs with tbi, Figure 11-1, Chapter 11: interfacing to other cores – Xilinx LOGICORE UG144 User Manual

Page 114: Discontinued product

114

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 11: Interfacing to Other Cores

R

-- DISCONTINUED PRODUCT --

Integration to Provide 1000BASE-X PCS with TBI

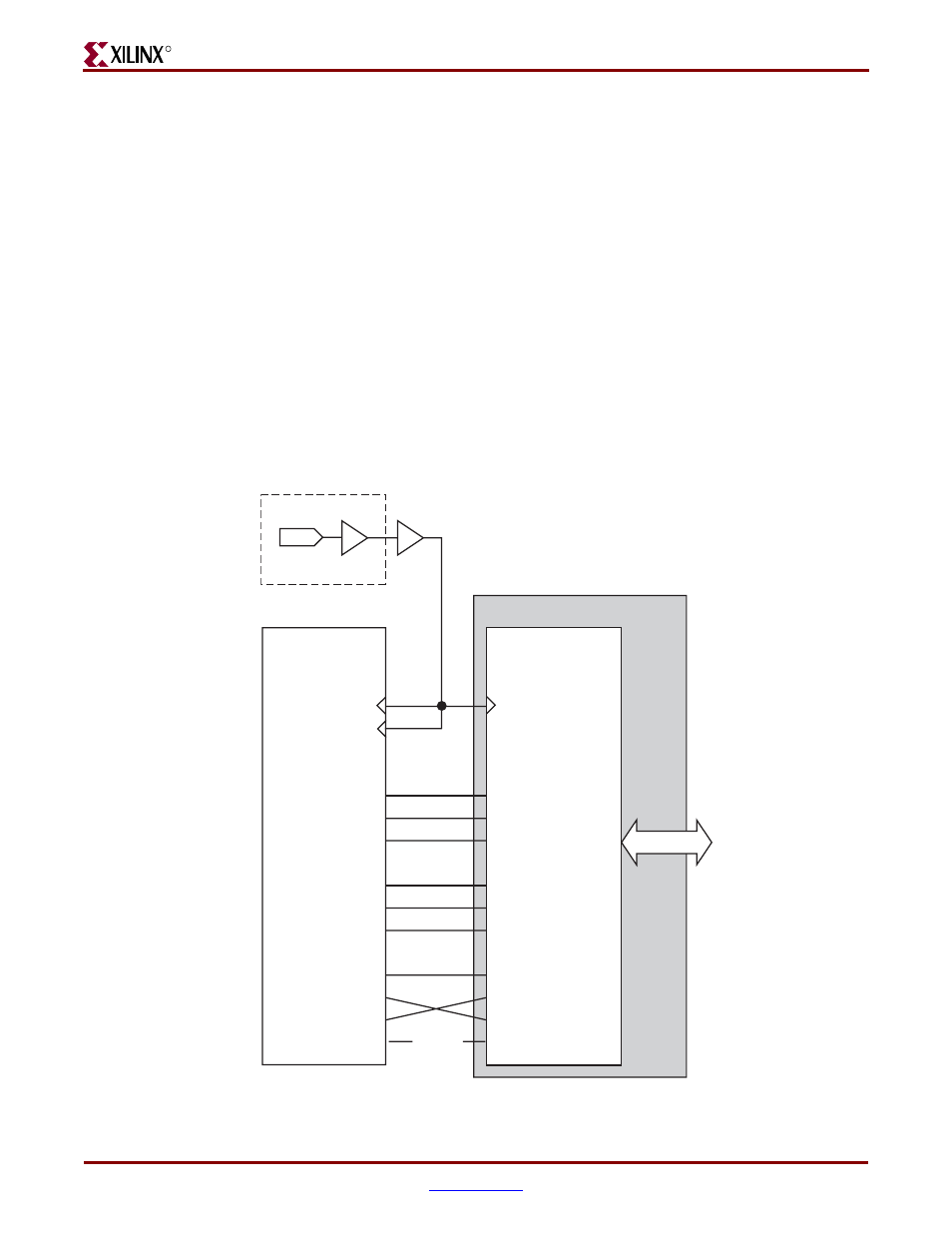

illustrates the connections and clock management logic required to interface

the GEMAC core to the Ethernet 1000BASE-X PCS/PMA or SGMII core (when used in

1000BASE-X mode with the parallel TBI). It depicts the following:

•

Direct internal connections are made between the GMII interfaces of the two cores.

•

If the GEMAC has been built with the optional management logic, the MDIO port can

be connected up to that of the Ethernet 1000BASE-X PCS/PMA or SGMII core to

access its embedded configuration and status registers. See

•

Due to the embedded Receiver Elastic Buffer in the Ethernet 1000BASE-X PCS/PMA

or SGMII core, the entire GMII is synchronous to a single clock domain. For this

reason, gtx_clk is used as the 125 MHz reference clock for both cores and the

transmitter and receiver logic of the GEMAC core now operate in the same clock

domain. This allows clock crossing constraints between the gtx_clk and

gmii_rx_clk

clock domains to be removed from the GEMAC user constraints file

(UCF). See

“Timespecs for Critical Logic within the Core.”

Figure 11-1:

1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS with TBI

1-Gigabit Ethernet

MAC

LogiCORE

gmii_rx_clk

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

gtx_clk

mdc

mdio_in

mdio_out

mdio_tri

Ethernet 1000BASE-X

PCS/PMA or SGMII

LogiCORE

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

mdc

mdio_in

mdio_out

mdio_tri

no

connection

gtx_clk

TBI

IPAD

IBUFG

IOB LOGIC

gtx_clk

gtx_clk_bufg (125 MHz)

BUFG

component_name_block

(Block Level from example design)