Table 8-5, Transmitter configuration – Xilinx LOGICORE UG144 User Manual

Page 80

80

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 8: Configuration and Status

R

-- DISCONTINUED PRODUCT --

Transmitter Configuration

The register contents for the Transmitter Configuration Word are described in

29

0

In-band FCS Enable

When this bit is ‘1,’ the MAC receiver

will pass the FCS field up to the client. When at ‘0,’ the

client will not be passed the FCS. In both cases, the FCS

will be verified on the frame.

30

0

Jumbo Frame Enable

When this bit is set to ‘1,’ the MAC

receiver will accept frames over the specified IEEE 802.3-

2005 maximum legal length. When this bit is ‘0,’ the MAC

will only accept frames up to the specified maximum.

31

0

Reset

When this bit is set to ‘1,’ the receiver will be reset.

The bit will then automatically revert to ‘0.’ This reset also

sets all of the receiver configuration registers to their

default values.

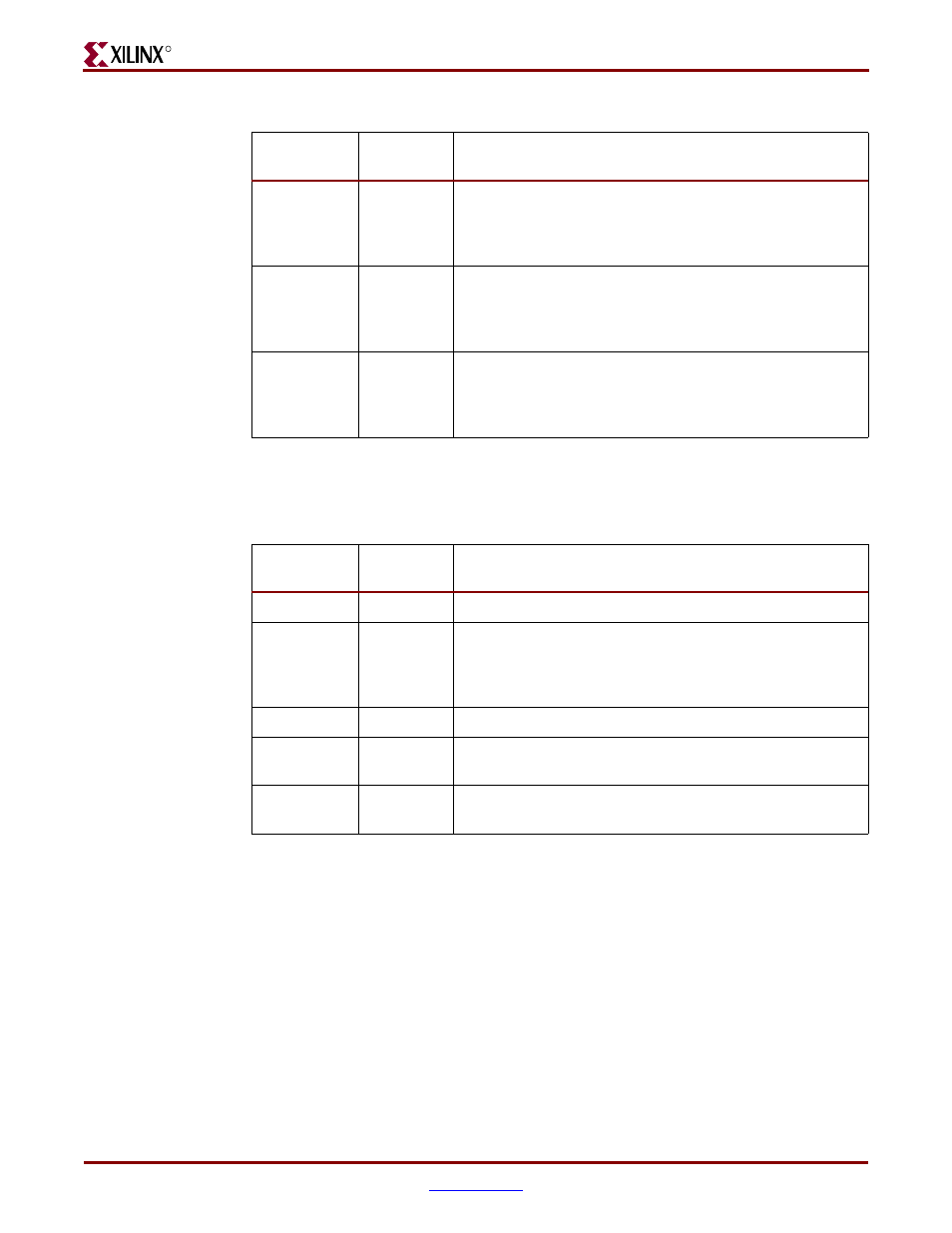

Table 8-4:

Receiver Configuration Word 1 (Continued)

Bit

Default

Value

Description

Table 8-5:

Transmitter Configuration Word

Bit

Default

Value

Description

24-0

n/a

Reserved

25

0

Interframe Gap Adjust Enable

If ‘1,’ the transmitter will

read the value on the port tx_ifg_delay at the start of frame

transmission and adjust the interframe gap following the

frame accordingly.

26

n/a

Reserved

27

0

VLAN Enable

When this bit is set to ‘1,’ the transmitter

will allow the transmission of VLAN tagged frames.

28

1

Transmit Enable

When this bit is ‘1,’ the transmitter is

operational. When it is ‘0,’ the transmitter is disabled.