Mdio interface, Figure 8-4, Mdio – Xilinx LOGICORE UG144 User Manual

Page 86: Introduction to mdio

86

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 8: Configuration and Status

R

-- DISCONTINUED PRODUCT --

MDIO Interface

Introduction to MDIO

The MDIO interface for 1 Gbps operation (and slower speeds) is defined in IEEE 802.3

clause 22. This is a two wire interface consisting of a clock, mdc, and a shared serial data

line, mdio.

An MDIO bus in a system consists of a single Station Management (STA) master

management entity and a number of MDIO Managed Device (MMD) slave entities.

illustrates a typical system. All transactions are initiated by the STA entity. The

GEMAC core implements a STA and can be connected to MMDs (PHY devices) to access

their management registers.

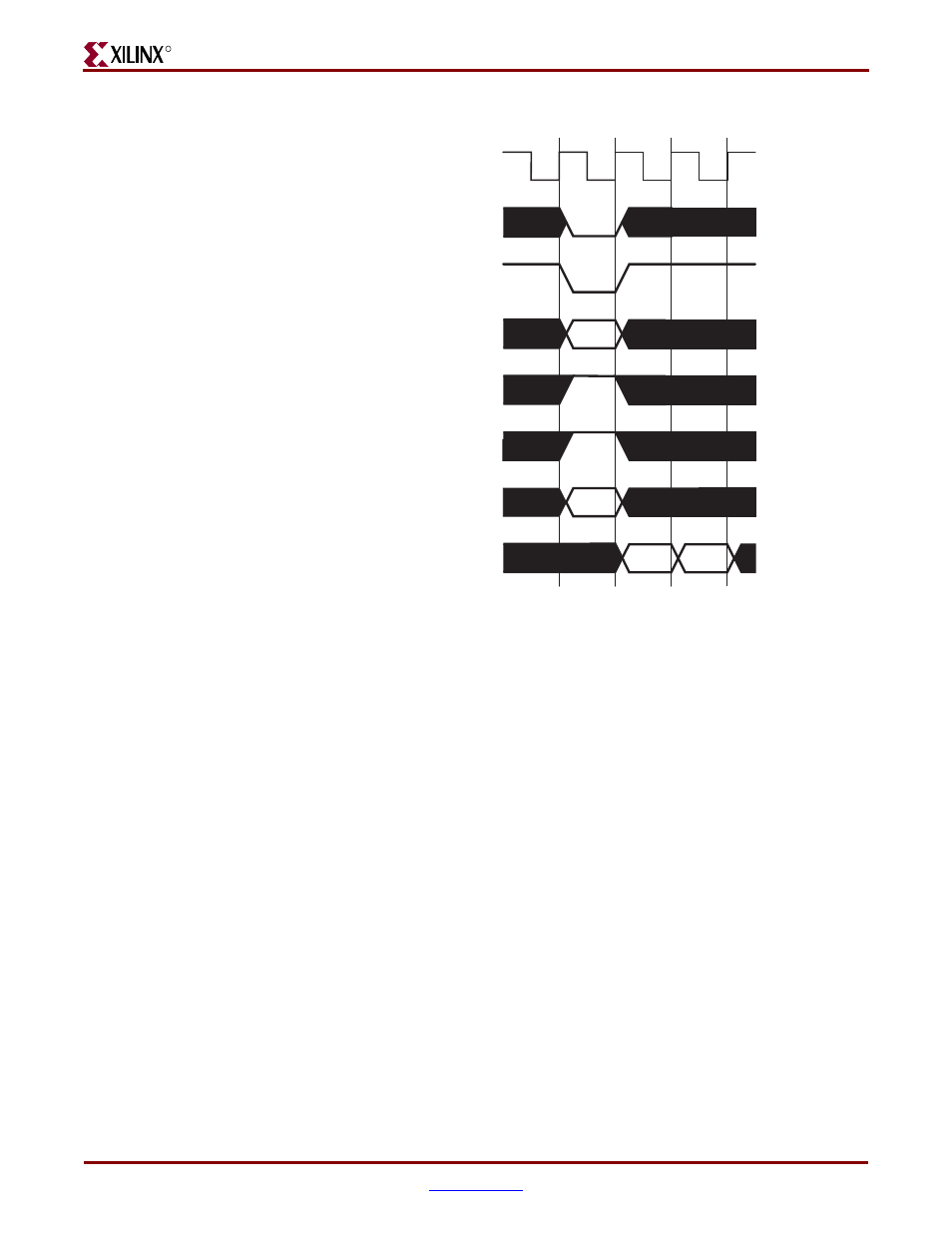

Figure 8-4:

Address Table Read Timing

hostclk

hostaddr[8:0]

hostaddr[9]

hostopcode[1]

hostmiimsel

hostrddata[31:0]

hostwrdata[23]

hostwrdata[17:16]

31 : 0

47 : 32

0x18C

LOCATION