Figure 8-3, Accessing the address table – Xilinx LOGICORE UG144 User Manual

Page 85

1-Gigabit Ethernet MAC v8.5 User Guide

85

UG144 April 24, 2009

Using the Optional Management Interface

R

-- DISCONTINUED PRODUCT --

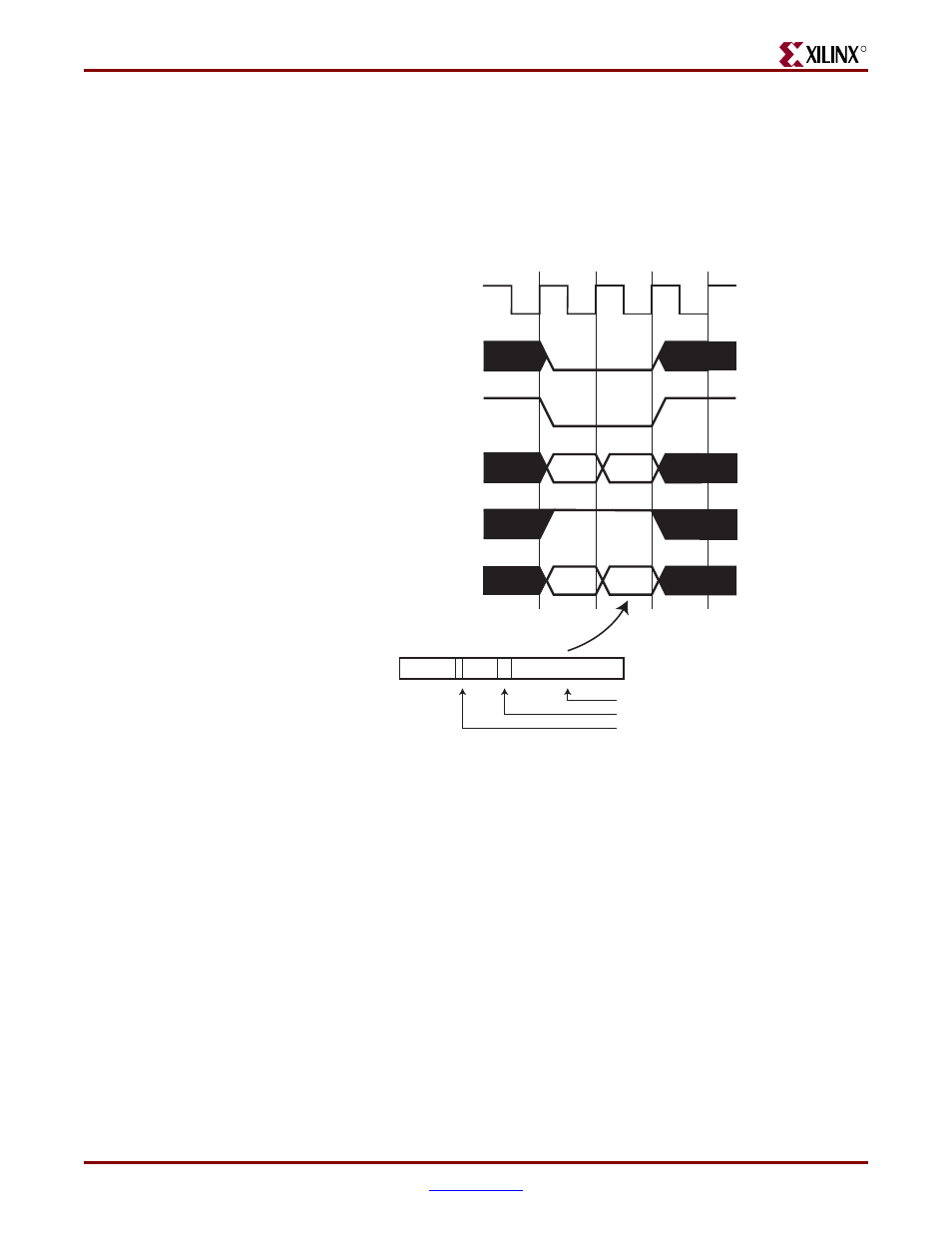

Accessing the Address Table

To write to a specific entry in the address table, you must first write the least significant 32-

bits of the address into the Address Table Configuration (Word 0) register. You then write

the most significant 16 bits together with the location in the table (bits 17–16) to the

Address Table Configuration (Word1) register with bit 23 (read not write) set to ‘0.’ This is

shown in

. Although it is shown in the figure, there is no requirement for the two

writes to be on adjacent cycles.

As shown in

, you must write to the Address Table Configuration register (Word

1) with the location set to the desired table entry and bit 23 set to ‘1’ to read from the

address table. On the next cycle the least significant word appears on the hostrddata

bus. One cycle afterwards, the most significant 16-bits are output on the lower 16 bits of the

bus.

Figure 8-3:

Address Table Write Timing

hostclk

hostaddr[8:0]

hostaddr[9]

hostopcode[1]

hostmiimsel

BITS15..0 = ADDR[47:32]

hostwrdata[31:0]

0x188

0x18C

ADDR[31:0]

BITS17..16 = LOCATION

BIT23 = 0

BIT31

BIT0