Figure 9-4, Ve edge – Xilinx LOGICORE UG144 User Manual

Page 107

1-Gigabit Ethernet MAC v8.5 User Guide

107

UG144 April 24, 2009

Required Constraints

R

-- DISCONTINUED PRODUCT --

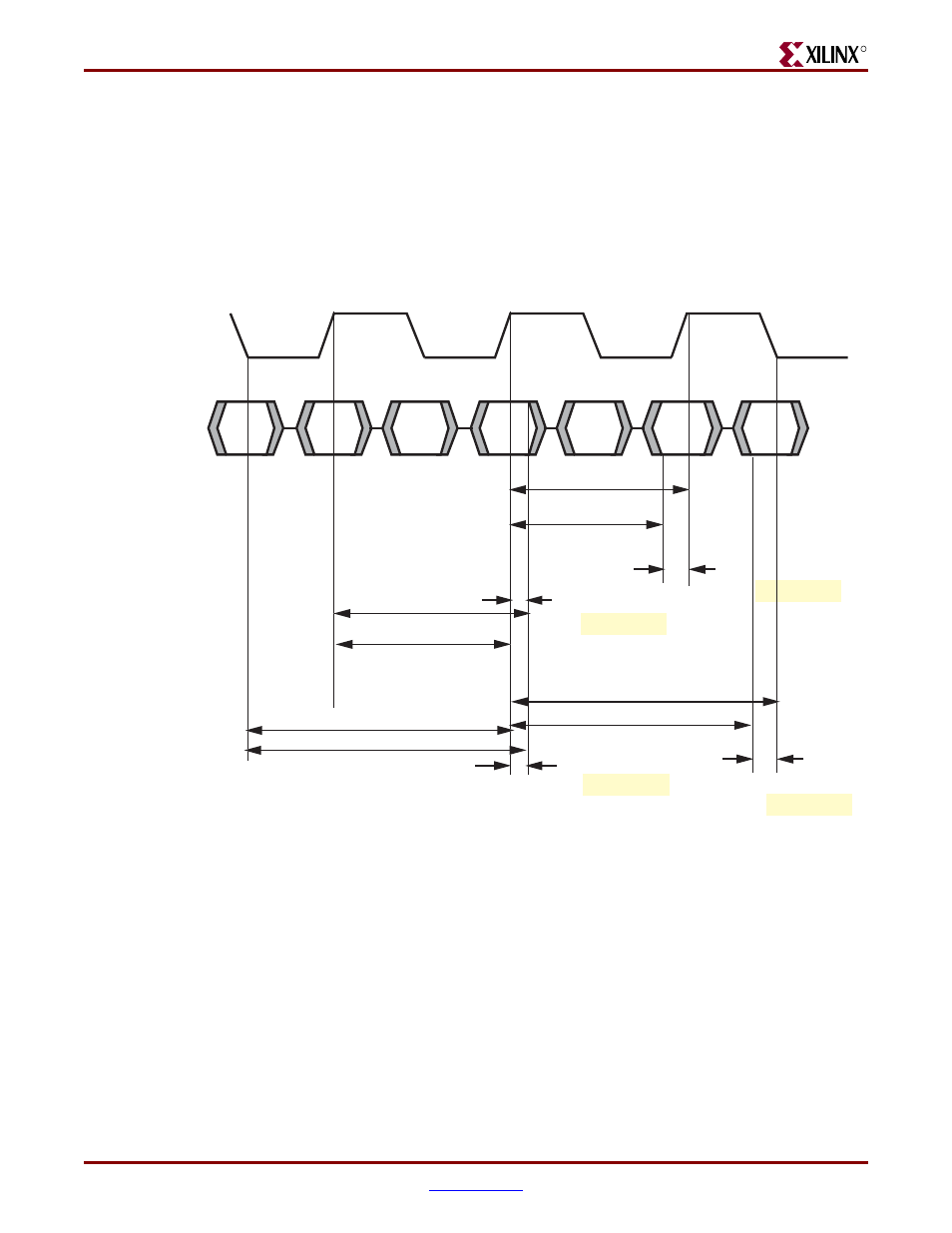

This is less than the 1 ns required, so there is slack. Equally for the –ve edge, we have

–11.179 ns of setup—this edge is at time 12 ns and therefore this equates to a setup of

0.821 ns.

The implementation requires 8.893 ns of hold to the +ve edge.

illustrates that

this represents 0.893 ns relative to the following rising edge of the clock (since the IDELAY

has acted to delay the clock by an entire period when measured from the input flip-flop).

This is less than the 1 ns required, so there is slack. Equally for the –ve edge, we have

12.893 ns of hold —this edge is at time 12 ns and therefore equates to a hold time of

0.893 ns.

Figure 9-4:

Timing Report Setup/Hold Illustration

t

SETUP

t

HOLD

RGMII_RXD[3:0],

RGMII_RX_CTL

RGMII_RXC

8 ns

-6.134 ns

= 8 - 7.179

= 0.821 ns

8 ns

8.893 ns

= 8.893 - 8

= 0.893 ns

12 ns

-11.179 ns

12 ns

12.893 ns

t

HOLD

= 12.893 - 12

= 0.893 ns

t

SETUP

= 12 - 11.179

= 0.821 ns