Figure 11-2, Virtex-4 devices, Ethernet 1000base-x pcs/pma or sgmii core – Xilinx LOGICORE UG144 User Manual

Page 115: Discontinued product

1-Gigabit Ethernet MAC v8.5 User Guide

115

UG144 April 24, 2009

Ethernet 1000Base-X PCS/PMA or SGMII Core

R

-- DISCONTINUED PRODUCT --

Integration to Provide 1000BASE-X PCS and PMA using a RocketIO

Transceiver

Virtex-4 Devices

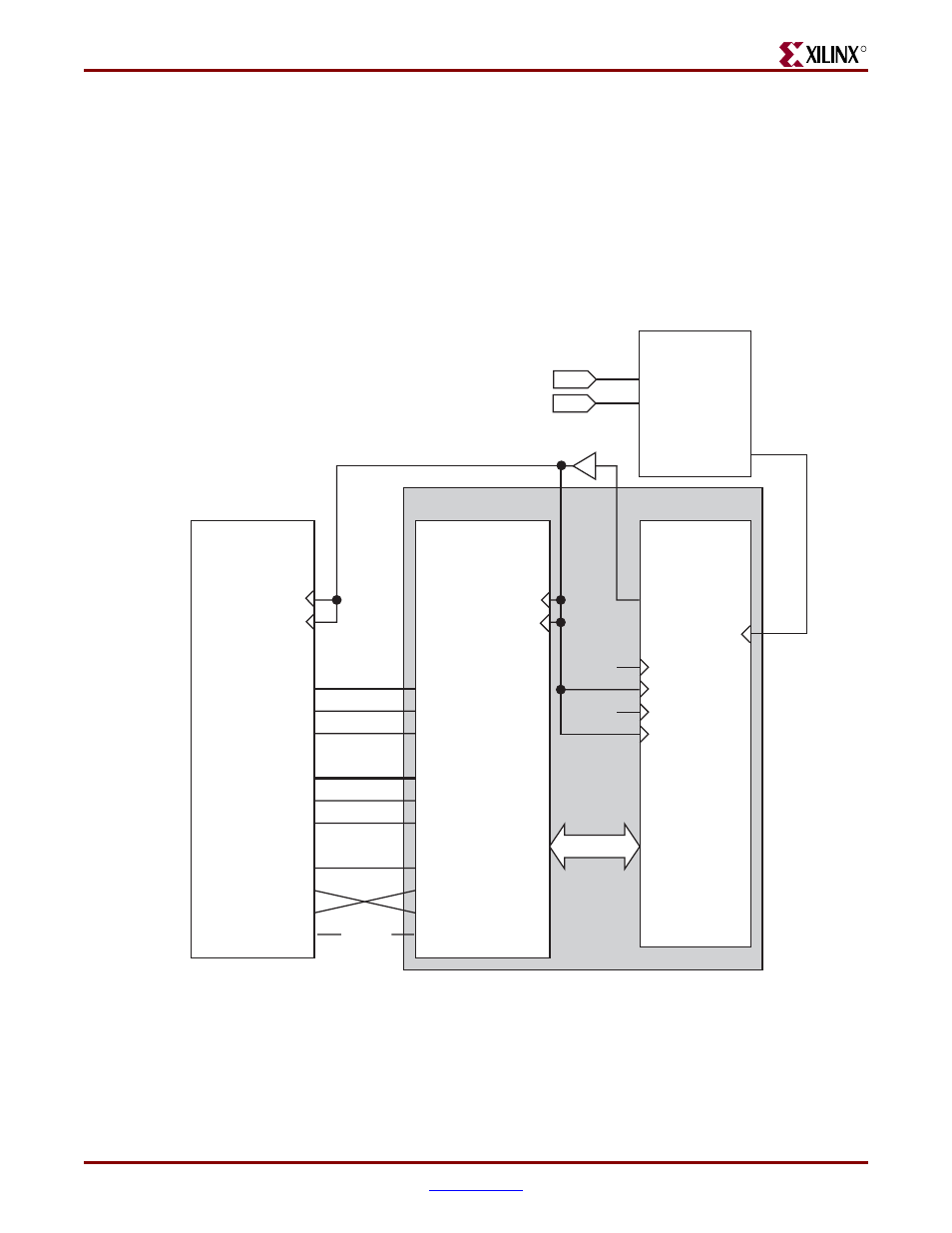

illustrates the connections and clock management logic required to interface

the GEMAC core to the Ethernet 1000BASE-X PCS/PMA or SGMII core (when used in

1000BASE-X mode with PMA using the device-specific RocketIO MGT transceiver.

Figure 11-2:

1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and PMA

using a RocketIO Transceiver

1-Gigabit Ethernet

MAC

LogiCORE

gmii_rx_clk

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

gtx_clk

mdc

mdio_in

mdio_out

mdio_tri

Ethernet 1000BASE-X

PCS/PMA or SGMII

LogiCORE

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

mdc

mdio_in

mdio_out

mdio_tri

Virtex-4

GT11

RocketIO

no

connection

userclk

userclk2

RocketIO I/F

IPAD

IPAD

brefclkn

(125 MHz)

Virtex-4

GT11CLK_MGT

MGTCLKP

MGTCLKN

SYNCLK1OUT

brefclkp

(125 MHz)

REFCLK1

userclk2

(125 MHz)

TXUSRCLK

TXUSRCLK2

RXUSRCLK

RXUSRCLK2

synclk1

(125MHz)

‘0’

‘0’

BUFG

TXOUTCLK1

component_name_block

(Block Level from example design)