Clocking and resetting, Clocking the core, With internal gmii – Xilinx LOGICORE UG144 User Manual

Page 109: With external gmii, Chapter 10: clocking and resetting, With internal gmii with external gmii, Figure 10-1, Chapter 10, “clocking and resetting, Chapter 10, “clocking and, Resetting

1-Gigabit Ethernet MAC v8.5 User Guide

109

UG144 April 24, 2009

R

-- DISCONTINUED PRODUCT --

Chapter 10

Clocking and Resetting

This chapter describes clock management considerations that are associated with

implementing the GEMAC core. It describes the clock management logic for all

implementations of the core and how clock management logic can be shared across

multiple instantiations of the core. The reset circuitry within the core is also described.

Clocking the Core

With Internal GMII

When the GMII-style interface of the core is used as an internal interface (for example, with

an internally connected PHY core), it is likely that gtx_clk and gmii_rx_clk will be

derived from the same clock source. See

Chapter 11, “Interfacing to Other Cores”

for an

example.

With External GMII

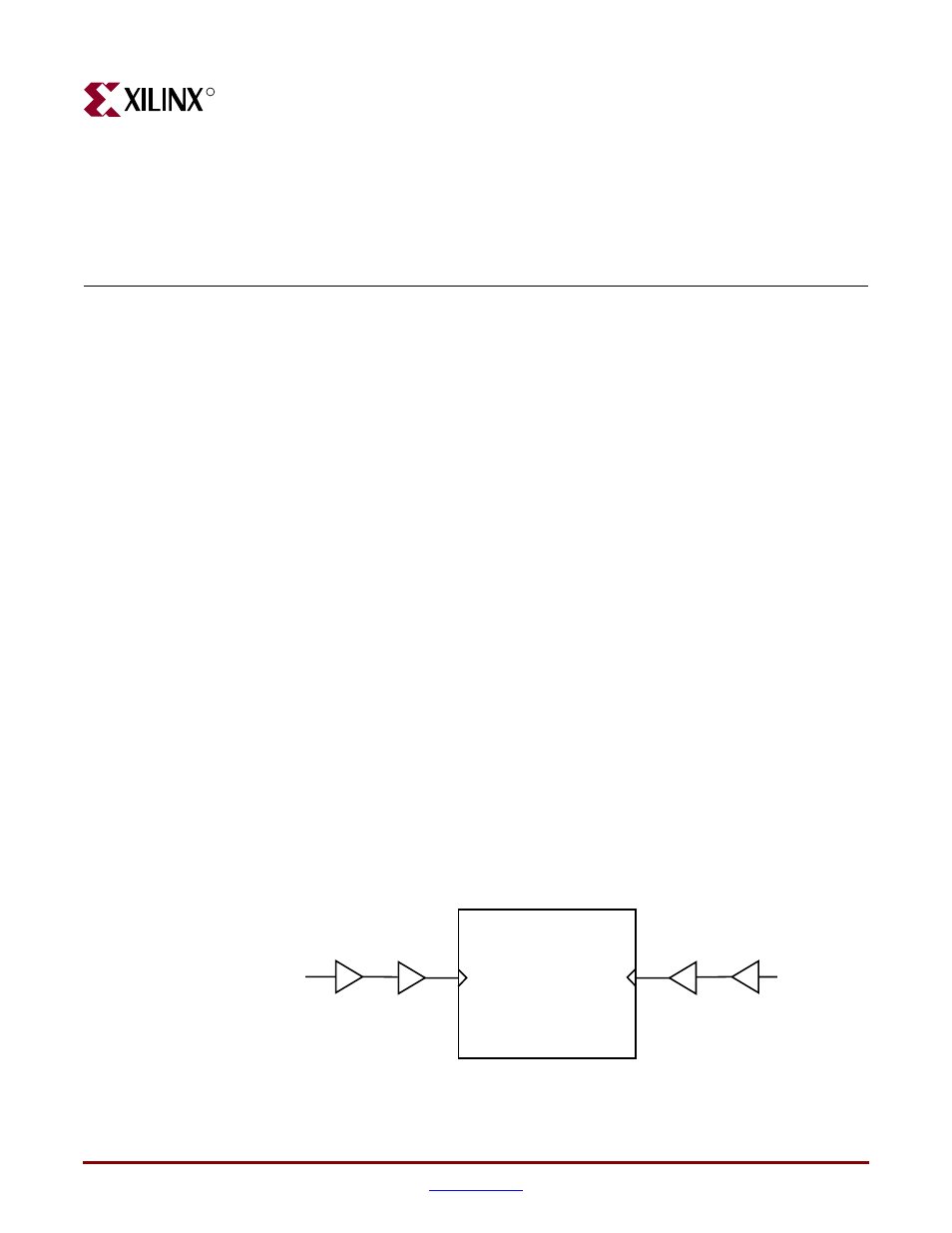

illustrates the clock management used with an external GMII interface. All

clocks illustrated have a frequency of 125 MHz. The clock gtx_clk must be provided to

the GEMAC core. This is a high-quality clock that satisfies the IEEE 802.3-2005

requirements. It is expected that this clock will be derived from an external oscillator and

connected into the device through an IBUFG, as illustrated in

When an external GMII, gmii_rx_clk will usually be derived from a different clock

source to gtx_clk. In this case, gmii_rx_clk is received through an IBUFG. This clock is

then usually routed onto a global clock network by connecting it to a BUFG. The resulting

global clock is used by all MAC receiver logic. Some families contain a DCM on the

gmii_rx_clk

path to meet GMII setup and hold requirements (see

3E, Spartan-3A and Virtex-4 Devices.”

)

Figure 10-1:

Clock Management Logic with External GMII

IBUFG

BUFG

1-Gigabit Ethernet MAC

gmii_rx_clk

gtx_clk

IBUFG

BUFG

gmii_rx_clk

gtx_clk