Figure 9-3, Table 9-2, Rgmii input setup/hold timing – Xilinx LOGICORE UG144 User Manual

Page 102

102

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 9: Constraining the Core

R

-- DISCONTINUED PRODUCT --

The RGMII v2.0 is a 1.5 volt signal-level interface. The 1.5 volt HSTL Class I SelectIO

standard is used for RGMII interface pins. Use the following constraints with the device IO

Banking rules. The IO slew rate is set to fast to ensure that the interface can meet setup and

hold times.

INST "rgmii_txd" IOSTANDARD = HSTL_I;

INST "rgmii_tx_ctl" IOSTANDARD = HSTL_I;

INST "rgmii_rxd" IOSTANDARD = HSTL_I;

INST "rgmii_rx_ctl" IOSTANDARD = HSTL_I;

INST "rgmii_txc" IOSTANDARD = HSTL_I;

INST "rgmii_rxc" IOSTANDARD = HSTL_I;

INST "rgmii_txd" SLEW = FAST;

INST "rgmii_tx_ctl" SLEW = FAST;

INST "rgmii_txc" SLEW = FAST;

In addition, the example design provides pad locking on the RGMII for several families.

This is provided as a guideline only; there are no specific I/O location constraints for this

core.

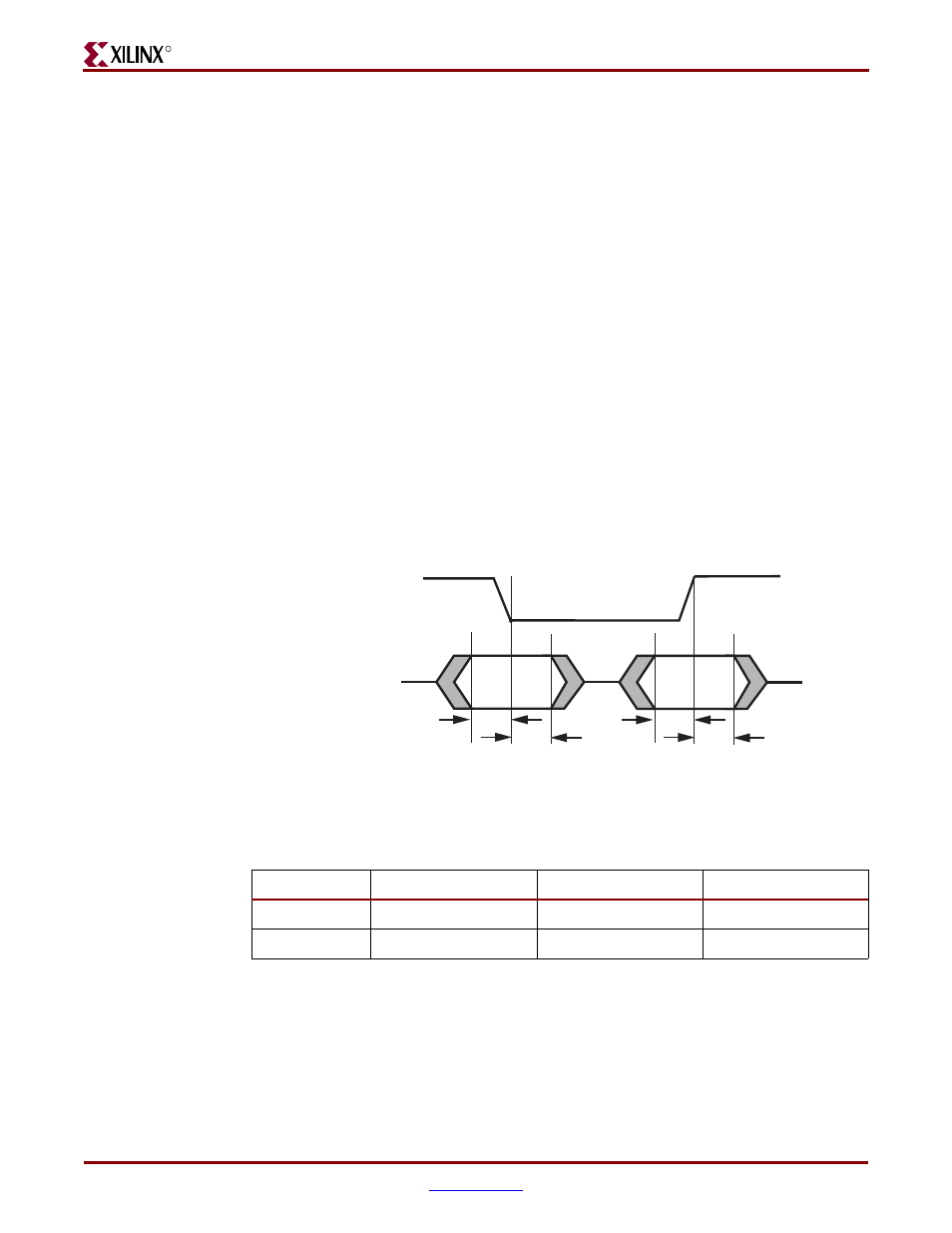

RGMII Input Setup/Hold Timing

illustrate the setup and hold time window for the input RGMII

signals. This is the worst-case data valid window presented to the FPGA device pins.

The 2 ns data valid window, which is presented across the RGMII input bus, must be

correctly sampled on both clock edges by the FPGA devices.

For RGMII, the lower data bits, rgmii_rxd[3:0], should be sampled internally on the

rising edge of rgmii_rxc, and the upper data bits, rgmii_rxd[7:4], should be

sampled internally on the falling edge of rgmii_rxc.

The following constraints are provided in the UCF for RGMII Example Designs. These

constraints invoke the tools to analyze the setup/hold requirements (though, if failing, the

tools are NOT capable of fixing them: meeting these constraints is a manual process - see

the following family specific sections for details):

Figure 9-3:

Input RGMII Timing

Table 9-2:

Input RGMII Timing

Symbol

Min

Typical

Units

t

SETUP

1.0

2.0

ns

t

HOLD

1.0

2.0

ns

t

SETUP

t

HOLD

t

SETUP

t

HOLD

RGMII_RXC

RGMII_RXD[3:0],

RGMII_RX_CTL