Figure 7-3, Virtex-5 devices, Implementing external gmii – Xilinx LOGICORE UG144 User Manual

Page 65: Discontinued product

1-Gigabit Ethernet MAC v8.5 User Guide

65

UG144 April 24, 2009

Implementing External GMII

R

-- DISCONTINUED PRODUCT --

Virtex-5 Devices

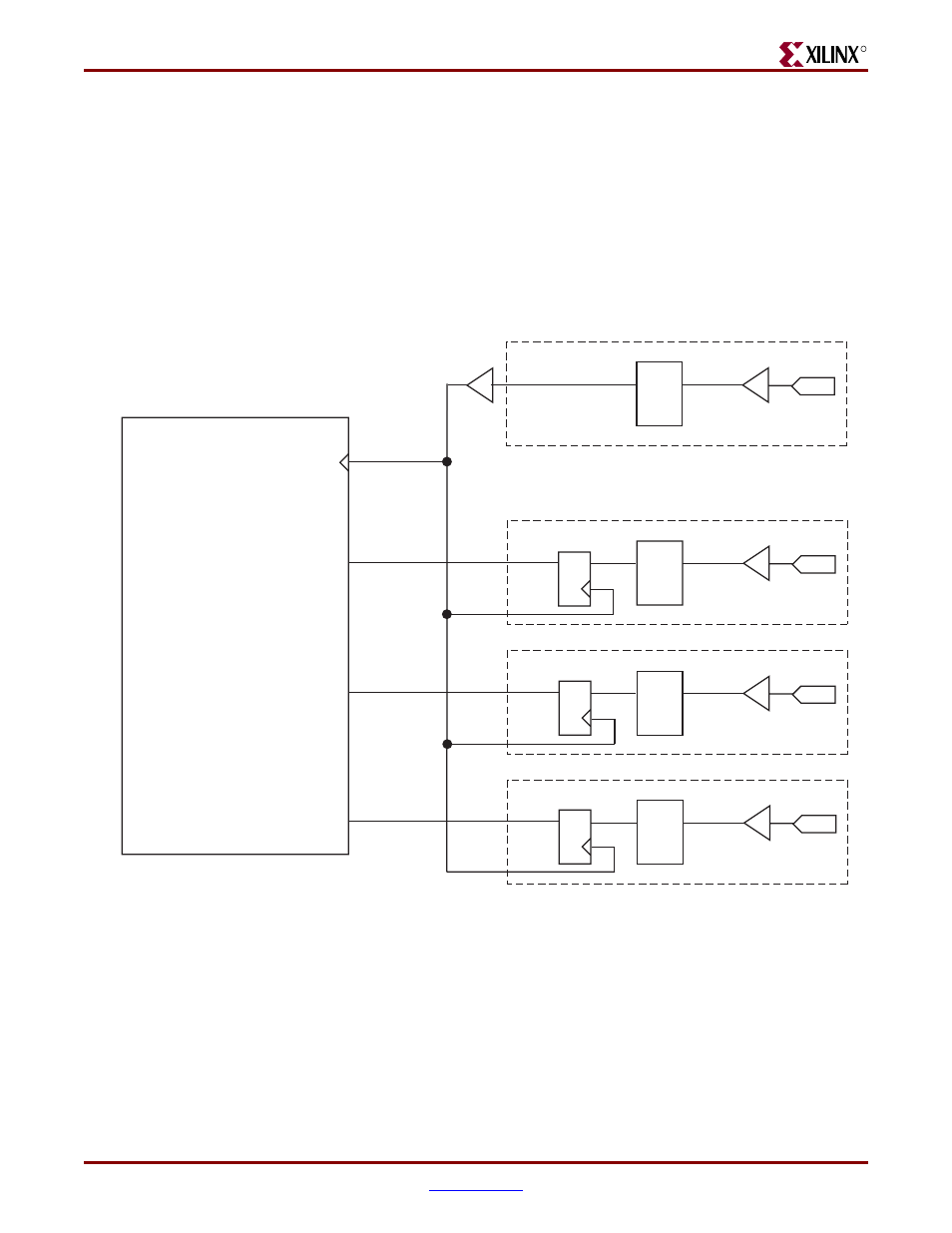

An IODELAY component may be used on the clock, data and control paths, as illustrated

in

. These can be used to either shift the input clock gmii_rx_clk or the data

and control signals to meet the setup and hold requirements of GMII and to allow for any

bus skew across the data and control inputs. The IODELAY components are used in fixed

delay mode, where the attribute IDELAY_VALUE determines the tap delay value. An

IDELAYCTRL primitive must be instantiated for this mode of operation. See the Virtex-5

FPGA User Guide for more information on the use of IDELAYCTRL and IODELAY

components.

Figure 7-3:

External GMII Receiver Logic for Virtex-5 Devices

gmii_rx_clk

IBUFG

IOB LOGIC

IPAD

gmii_rxd[0]

IBUF

IPAD

D

Q

gmii_rx_dv

IBUF

IPAD

gmii_rx_er

IBUF

IPAD

1-Gigabit Ethernet MAC LogiCORE

gmii_rxd_reg[0]

gmii_rx_dv_reg

gmii_rx_er_reg

gmii_rx_clk

gmii_rxd[0]

gmii_rx_dv

gmii_rx_er

D

Q

D

Q

BUFG

IODELAY

IODELAY

IODELAY

IODELAY