Constraints when implementing an external rgmii, Figure 9-2, Rgmii iob constraints – Xilinx LOGICORE UG144 User Manual

Page 101

1-Gigabit Ethernet MAC v8.5 User Guide

101

UG144 April 24, 2009

Required Constraints

R

-- DISCONTINUED PRODUCT --

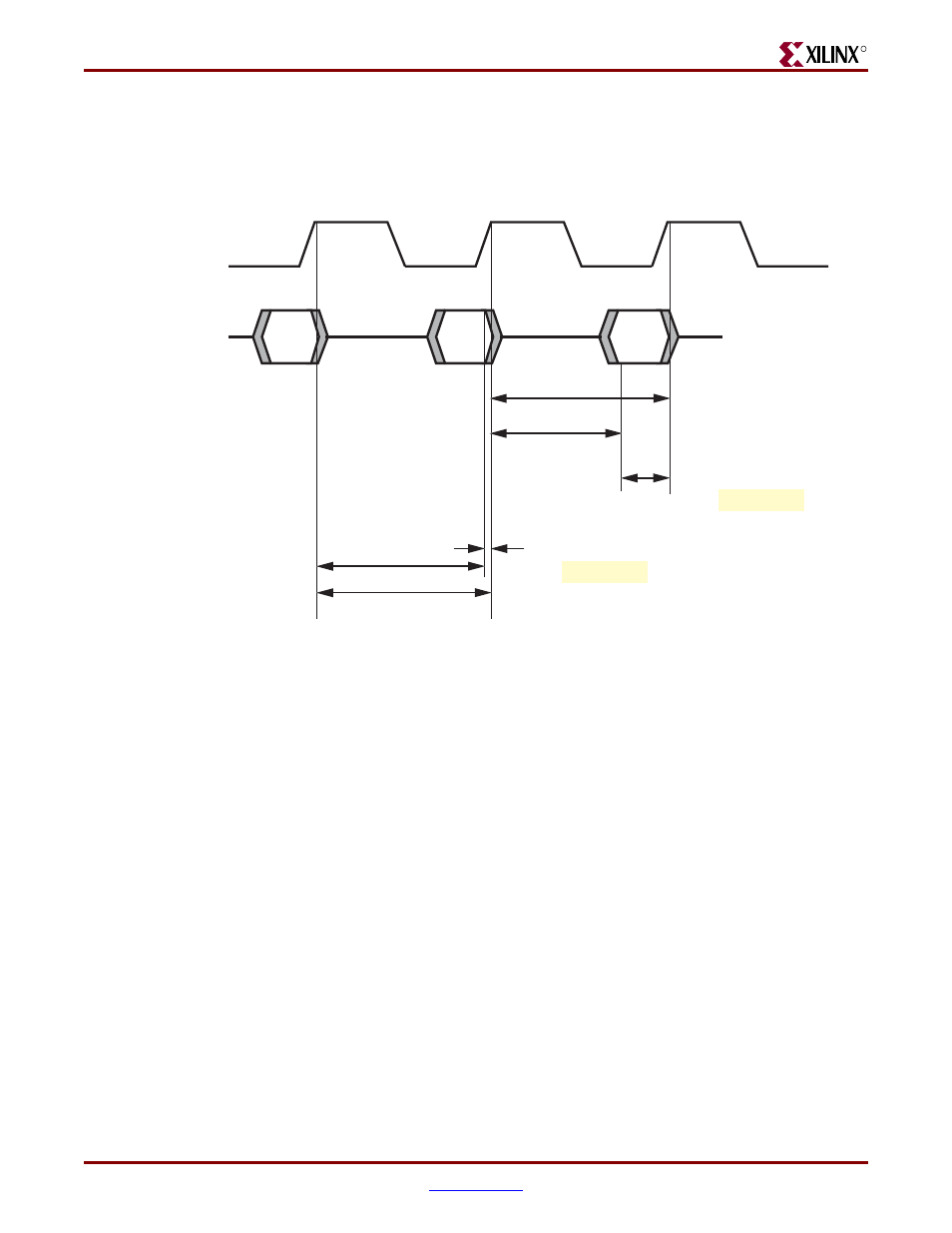

The implementation requires 7.554 ns of hold.

illustrates that this represents a

figure of -0.446 ns relative to the following rising edge of the clock (since the IDELAY has

acted to delay the clock by an entire period when measured from the input flip-flop). This

is less than the 0 ns required so there is slack.

Constraints when Implementing an External RGMII

The constraints defined in this section are implemented in the UCF for the example design

delivered with the core. Sections from this UCF are copied into the following descriptions

to provide examples. These examples should be studied in conjunction with the HDL

source code for the example design and with the description

.

RGMII IOB Constraints

The following constraints target the flip-flops that are inferred in the top-level HDL file for

the example design. Constraints are set to ensure that these are placed in IOBs. The DDR

register constraints are not present for a Virtex-4 device or Virtex-5 device where DDR

components are instantiated rather than inferred.

# RGMII Receiver Constraints: place DDR registers in IOB

INST "*rgmii_interface/rgmii_rxd_ddr*" IOB = true;

INST "*rgmii_interface/rgmii_rx_dv_ddr" IOB = true;

INST "*rgmii_interface/rgmii_rx_ctl_ddr" IOB = true;

# Inband Status Registers: place registers in IOB

INST "*rgmii_interface/link_status" IOB = true;

INST "*rgmii_interface/clock_speed*" IOB = true;

INST "*rgmii_interface/duplex_status" IOB = true;

Figure 9-2:

Timing Report Setup/Hold Illustration

t

SETUP

t

HOLD

GMII_RXD[7:0],

GMII_RX_DV

GMII_RX_ER

GMII_RX_CLK

8 ns

-6.134 ns

= 8 - 6.134

= 1.866 ns

8 ns

7.554 ns

= 7.554 - 8

= -0.446 ns