Figure 4-1 – Xilinx LOGICORE UG144 User Manual

Page 36

36

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 4: Designing with the Core

R

-- DISCONTINUED PRODUCT --

Using the example design as a starting point, you can do the following:

•

Edit the HDL top level of the example design file to:

♦

Change the clocking scheme.

♦

Add/remove IOBs as required.

♦

Replace the client loopback logic with your specific application logic.

♦

Adapt the 10 Mbps, 100 Mbps, 1 Gbps Ethernet FIFO to suit your specific

application (see

•

Synthesize the entire design.

The Xilinx Synthesis Tool (XST) script and Project file in the /implement directory

may be adapted to include any HDL files you may want to add.

•

Run the implement script in the /implement directory to create a top-level netlist for

the design. The script may also run the Xilinx tools map, par, and bitgen, creating a

bitstream that can be downloaded to a Xilinx device. SimPrim-based simulation

models for the entire design are also produced by the implement scripts.

•

Simulate the entire design using the demonstration test bench provided as a template

in the /simulation directory.

•

Download the bitstream to a target device.

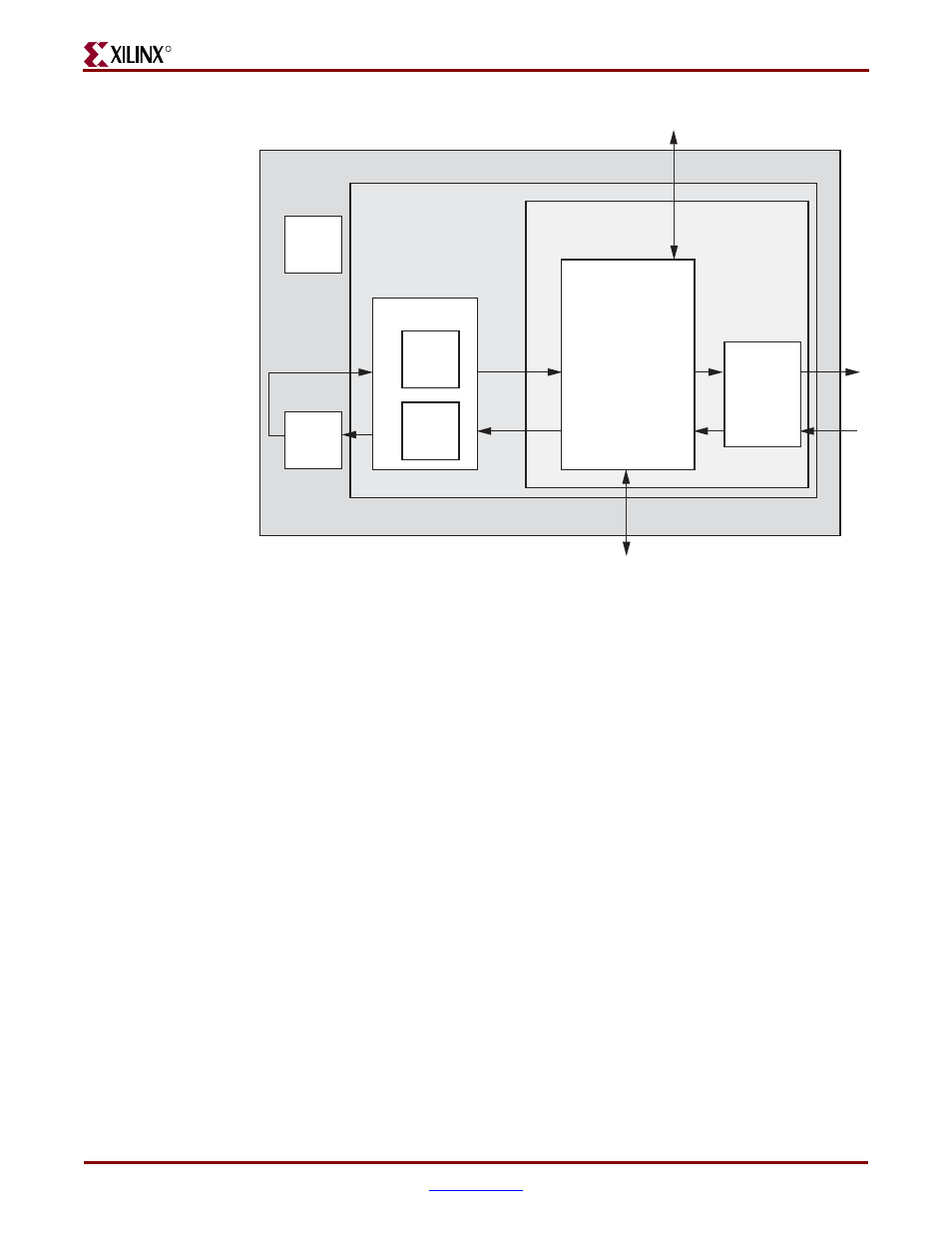

Figure 4-1:

1-Gigabit Ethernet MAC Core Example Design

GMII/ RGMII

Interface

Logic,

IOBs and

Clock

Management

Client

Interface

10 Mbps, 100 Mbps

1 Gbps Ethernet FIFO

1-Gigabit Ethernet

MAC Core

Management

Interface

Statistics Vectors

Interface

Tx Client

FIFO

Rx Client

FIFO

Physical

Interface

Address

Swap

Module

Clock/

Reset

Circuitry

LocalLink Interf

ace