With rgmii, Multiple cores, With external gmii – Xilinx LOGICORE UG144 User Manual

Page 110: Figure 10-2, Standard clocking scheme

110

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 10: Clocking and Resetting

R

-- DISCONTINUED PRODUCT --

With RGMII

Standard Clocking Scheme

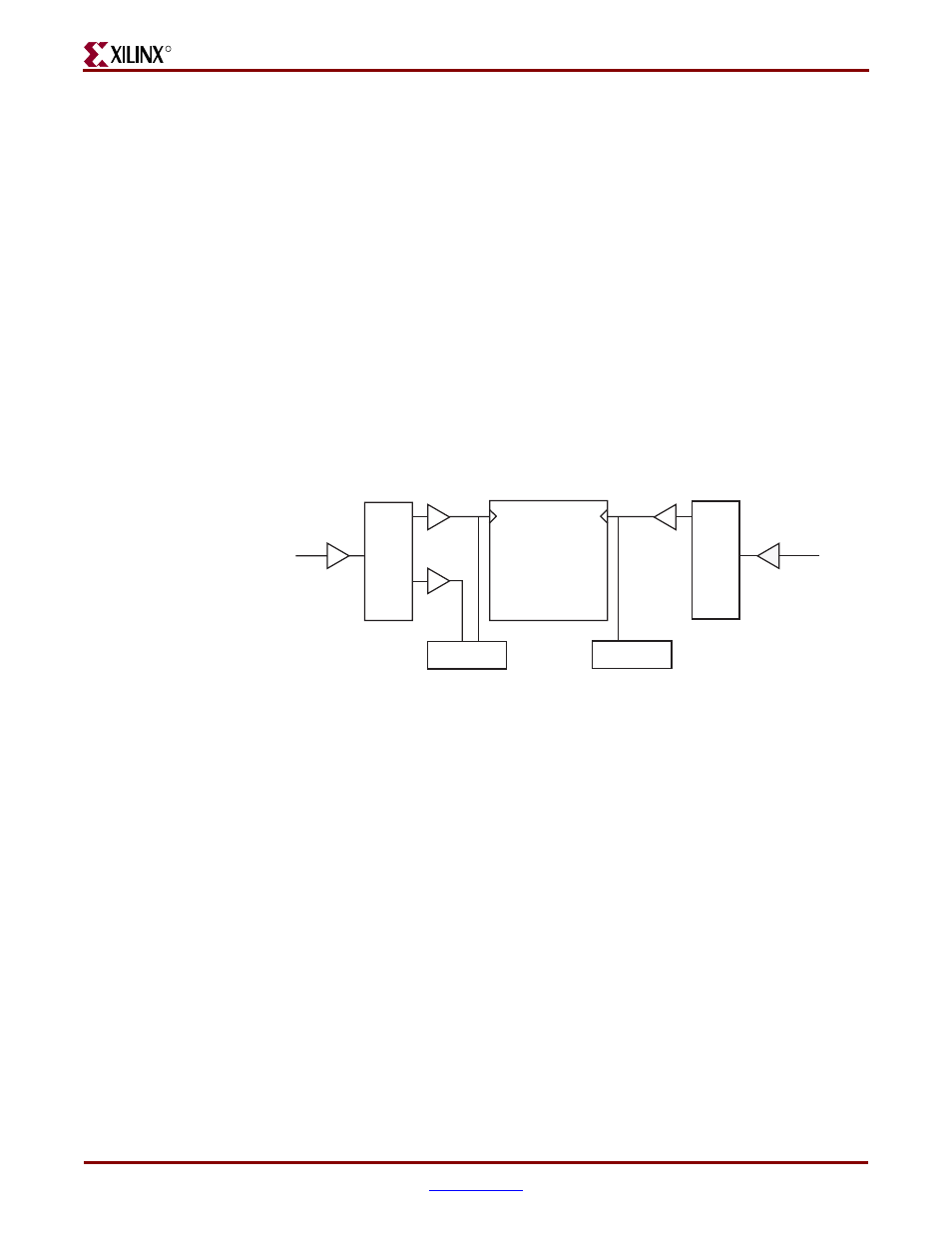

illustrates the clock management used with an external RGMII interface. All

clocks illustrated have a frequency of 125 MHz. The gtx_clk clock must be provided to

the GEMAC core. This is a high-quality clock that satisfies IEEE 802.3-2005 requirements. It

is expected that this clock will be derived from an external oscillator and connected into the

device through an IBUFG as illustrated in

. This clock is used as the input clock

to a DCM from where phase-shifted clock signals are generated for use in the RGMII

transmitter logic. The zero phase-shifted clock is used as the input gtx_clk to the

GEMAC core.

The receiver clock, rgmii_rxc is usually derived from a different clock source to

gtx_clk

. In this case, rgmii_rxc will be received through an IBUFG. This clock is routed

into a DCM where it is used to generate phase-shifted clock signals for use in the RGMII

receiver logic. A fixed phase-shift value is applied to the DCM to meet RGMII setup and

hold requirements. See

Appendix C, “Calculating DCM Phase-Shifting.”

The zero clock is

used as the input gmii_rx_clk to the GEMAC core.

Multiple Cores

With External GMII

illustrates how to share clock resources across multiple instantiations of the

core when using the optional GMII. gtx_clk may be shared between multiple cores as

illustrated, resulting in a common transmitter clock domain across the device.

A common receiver clock domain is usually not possible as each core will receive an

independent receiver clock from the PHY attached to the other end of the GMII. As

illustrated in

, this results in a separate receiver clock domain for each core.

Figure 10-2:

Clock Management with External RGMII

IBUFG

BUFG

gtx_clk

rgmii_rxc

1-Gigabit Ethernet

MAC Core

gmii_rx_clk

gtx_clk

IBUFG

BUFG

CLK_0

CLK_90

DCM

CLK_0

DCM

RGMII Tx Logic

RGMII Rx Logic

BUFG