Gmii receiver logic, Figure 7-2 – Xilinx LOGICORE UG144 User Manual

Page 63

1-Gigabit Ethernet MAC v8.5 User Guide

63

UG144 April 24, 2009

Implementing External GMII

R

-- DISCONTINUED PRODUCT --

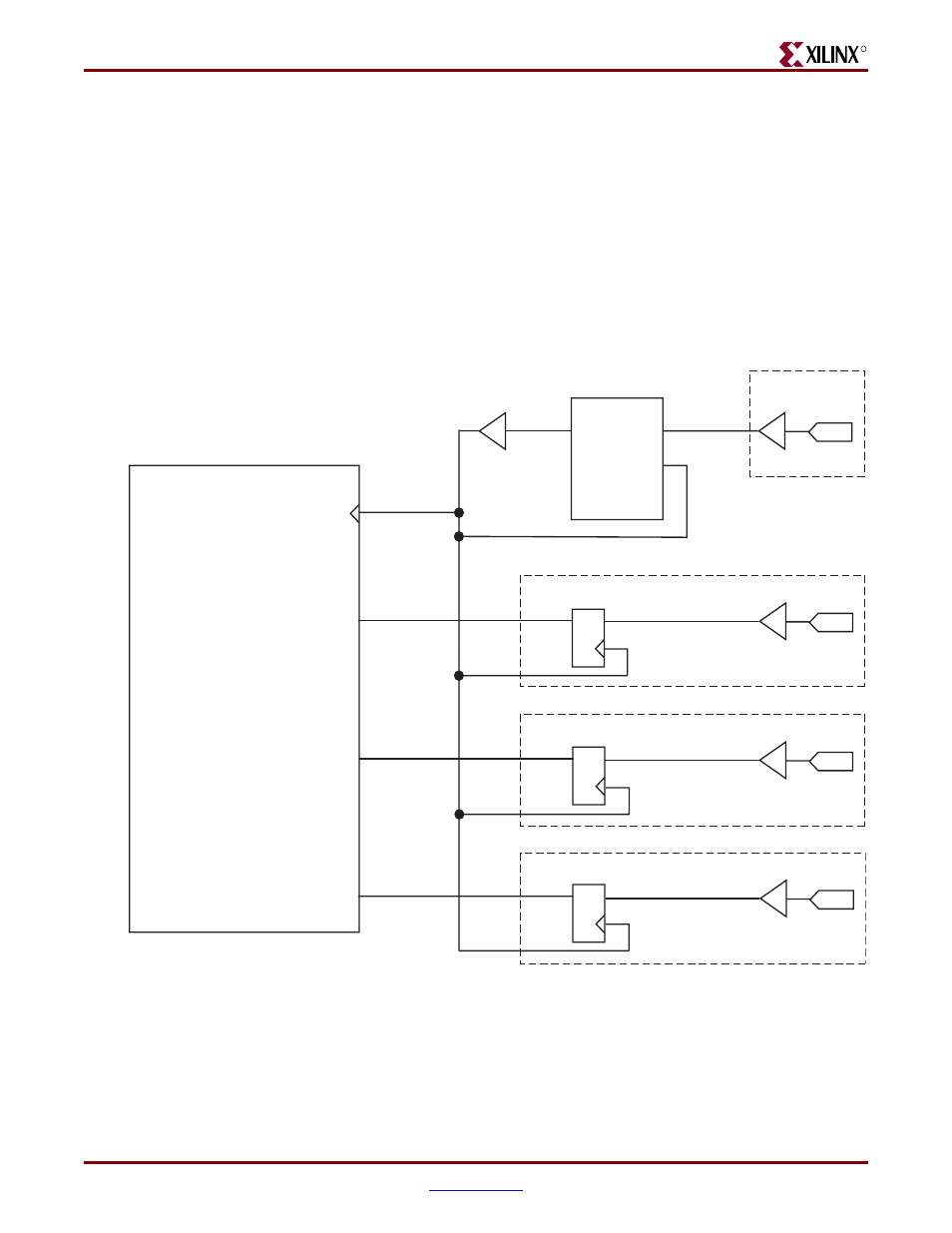

GMII Receiver Logic

Spartan-3, Spartan-3E, Spartan-3A and Virtex-4 Devices

A DCM must be used on the gmii_rx_clk clock path, as illustrated in

, to meet

the input setup and hold requirements for GMII. This is performed by the example designs

delivered with the core (all signal names and logic match

). This DCM circuitry

may optionally be used in other families.

Phase-shifting may then be applied to the DCM to fine-tune the setup and hold times at the

GMII IOB input flip-flops. Fixed phase-shift is applied to the DCM with the example UCF

for the example design. See

Appendix C, “Calculating DCM Phase-Shifting.”

Figure 7-2:

External GMII Receiver Logic for Spartan-3, Spartan-3E, and Spartan-3A Devices

gmii_rx_clk

IBUFG

IOB LOGIC

IPAD

gmii_rxd[0]

IBUF

IPAD

D

Q

gmii_rx_dv

IBUF

IPAD

gmii_rx_er

IBUF

IPAD

1-Gigabit Ethernet MAC LogiCORE

gmii_rxd_reg[0]

gmii_rx_dv_reg

gmii_rx_er_reg

gmii_rx_clk

gmii_rxd[0]

gmii_rx_dv

gmii_rx_er

D

Q

D

Q

BUFG

IOB LOGIC

DCM

CLKIN

CLK0

FB

gmii_rx_clk0

gmii_rx_clk_bufg