Configuration and status, Using the optional management interface, Host clock frequency – Xilinx LOGICORE UG144 User Manual

Page 77: Chapter 8: configuration and status, Table 8-1, Chapter 8, “configuration and status, Using the optional, Chapter 8

1-Gigabit Ethernet MAC v8.5 User Guide

77

UG144 April 24, 2009

R

-- DISCONTINUED PRODUCT --

Chapter 8

Configuration and Status

This chapter provides general guidelines for configuring and monitoring the GEMAC

core, including a detailed description of the client-side management interface and registers

present in the core. It also describes the alternative to the optional management interface

which is the Configuration Vector.

Using the Optional Management Interface

The Management Interface is a processor-independent interface with standard address,

data, and control signals. It may be used as is, or a wrapper (not supplied) may be used to

interface to common bus architectures. For port definition, see

This interface is used for:

•

Configuring of the GEMAC core via the configuration registers.

•

Access through the MDIO interface to the management registers located in the PHY

connected to the GEMAC core.

The Management Interface can be accessed in different ways, depending on the type of

transaction. A truth table showing which access method is required for each transaction

type is shown in

. These access methods are described in the following sections.

Host Clock Frequency

The Management Interface clock, host_clk, is used to derive the MDIO clock, mdc, and

for this reason is subject to the following frequency restriction:

≥

10 MHz

Configuring the GEMAC core to derive the mdc signal from this clock is detailed in

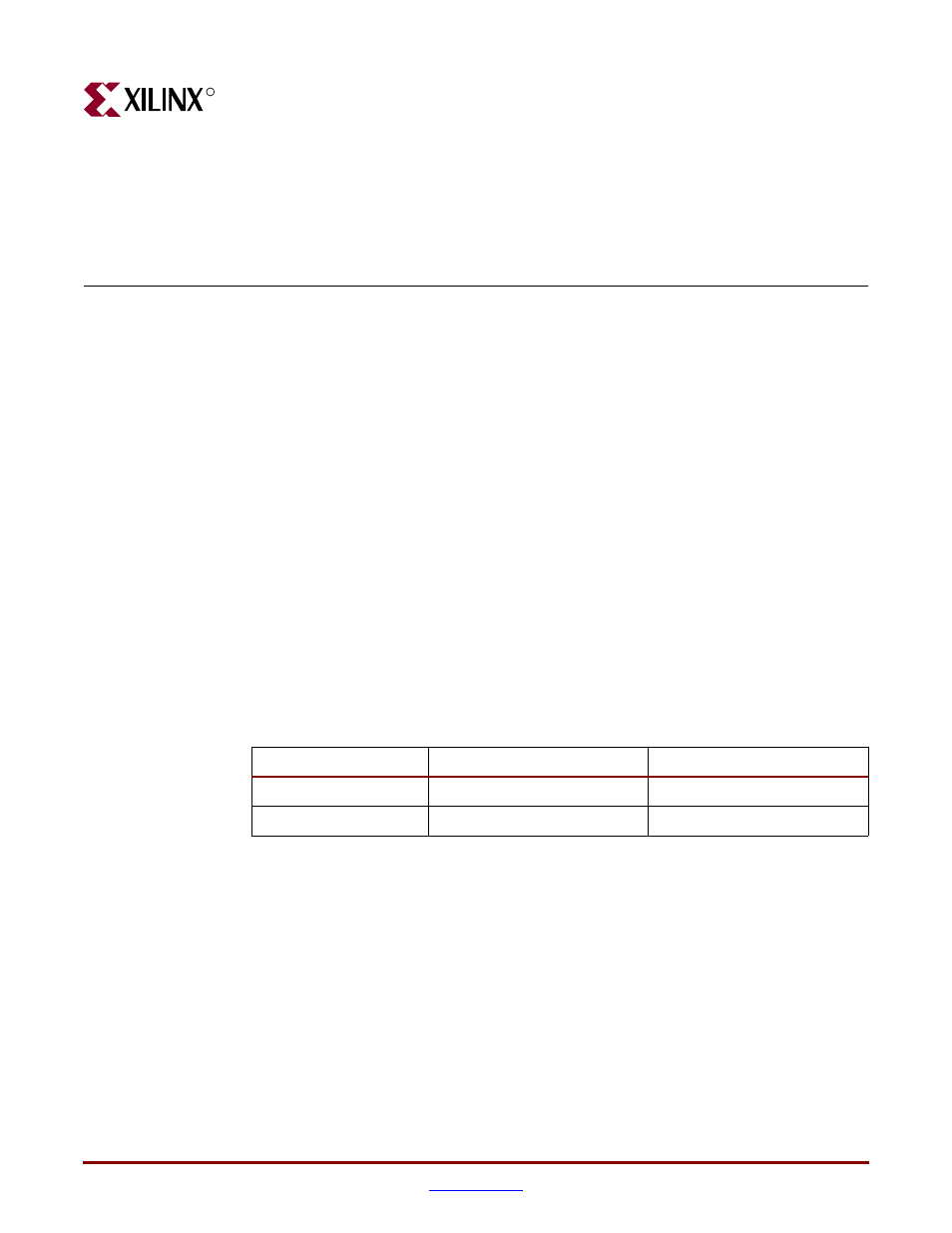

Table 8-1:

Management Interface Transaction Types

Transaction

host_miim_sel

host_addr[9]

Configuration

0

1

MIIM access

1

X