Receive fifo, Table a-3, Table a-4 – Xilinx LOGICORE UG144 User Manual

Page 129

1-Gigabit Ethernet MAC v8.5 User Guide

129

UG144 April 24, 2009

Interfaces

R

-- DISCONTINUED PRODUCT --

Receive FIFO

describes the receive FIFO client interface. For more information on the MAC

client interface, see

“Receiving Inbound Frames,” on page 39

describes the receive FIFO LocalLink interface. For more information on the

LocalLink interface, see

“Overview of LocalLink Interface,” on page 130

.

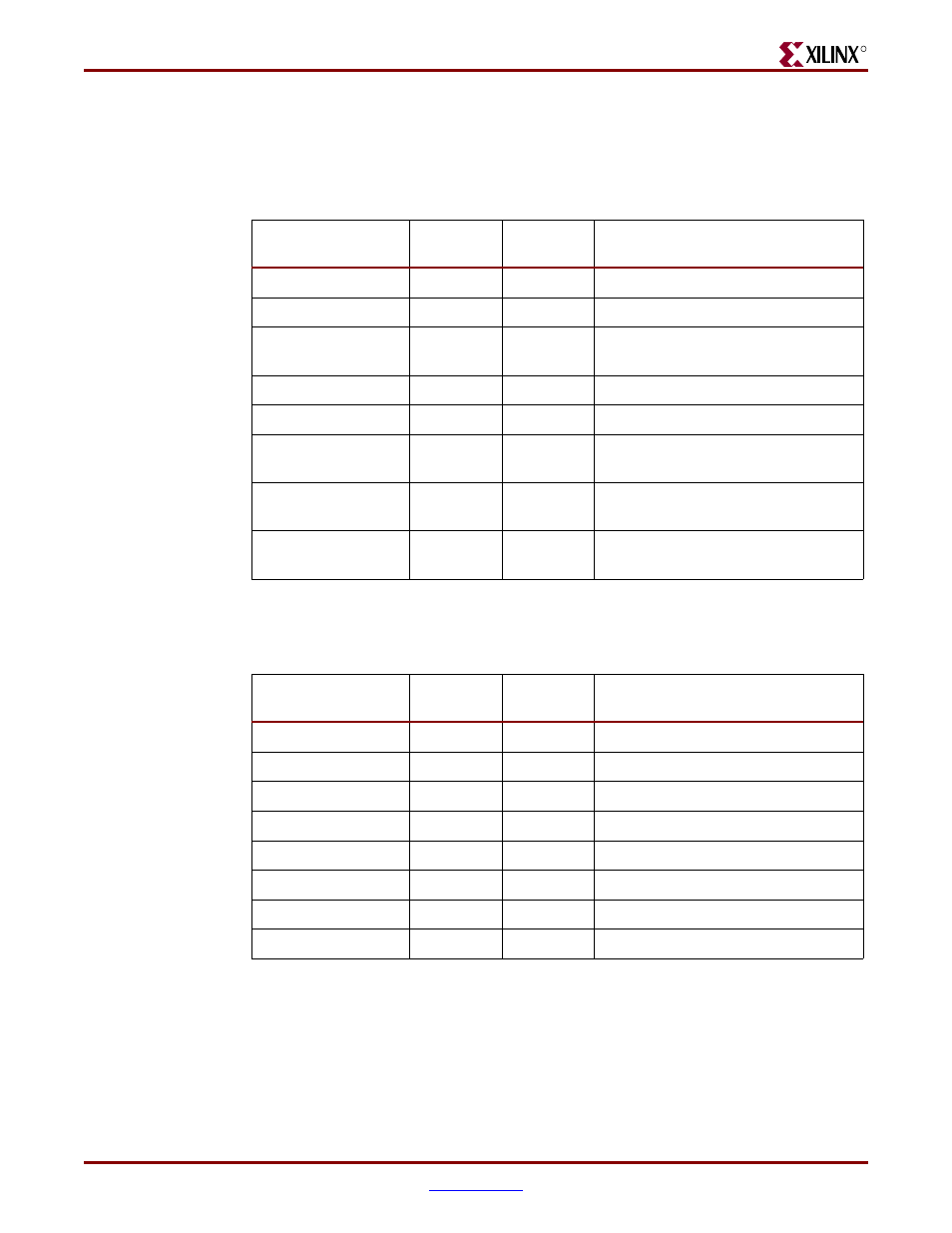

Table A-3:

Receive FIFO Client Interface

Signal

Direction

Clock

Domain

Description

rx_clk

Input

N/A

Receive clock used by MAC

rx_reset

Input

rx_clk

Synchronous reset

rx_enable

Input

rx_clk

Clock enable for rx_clk, tie to logic 1

when using GEMAC

rx_data[7:0]

Input

rx_clk

Data received from MAC

rx_data_valid

Input

rx_clk

Valid signal for data

rx_good_frame

Input

rx_clk

Indicates if frame is valid and should

be accepted by client

rx_bad_frame

Input

rx_clk

Indicates if frame is invalid and

should be dropped by the FIFO

rx_overflow

Output

rx_clk

Overflow signal indicates when a

frame has been dropped in the FIFO

Table A-4:

Receive FIFO LocalLink Interface

Signal

Direction

Clock

Domain

Description

rx_ll_clock

Input

N/A

Read clock for LocalLink interface

rx_ll_reset

Input

rx_ll_clock

Synchronous reset

rx_ll_data_out[7:0]

Output

rx_ll_clock

Data read from FIFO

rx_ll_sof_out_n

Output

rx_ll_clock

Start of frame indicator

rx_ll_eof_out_n

Output

rx_ll_clock

End of frame indicator

rx_ll_src_rdy_out_n

Output

rx_ll_clock

Source ready indicator

rx_ll_dst_rdy_in_n

Input

rx_ll_clock

Destination ready indicator

rx_fifo_status[3:0]

Output

rx_ll_clock

FIFO memory status