Figure 11-4, Virtex-5 fxt devices, Chapter 11: interfacing to other cores – Xilinx LOGICORE UG144 User Manual

Page 118

118

1-Gigabit Ethernet MAC v8.5 User Guide

UG144 April 24, 2009

Chapter 11: Interfacing to Other Cores

R

-- DISCONTINUED PRODUCT --

•

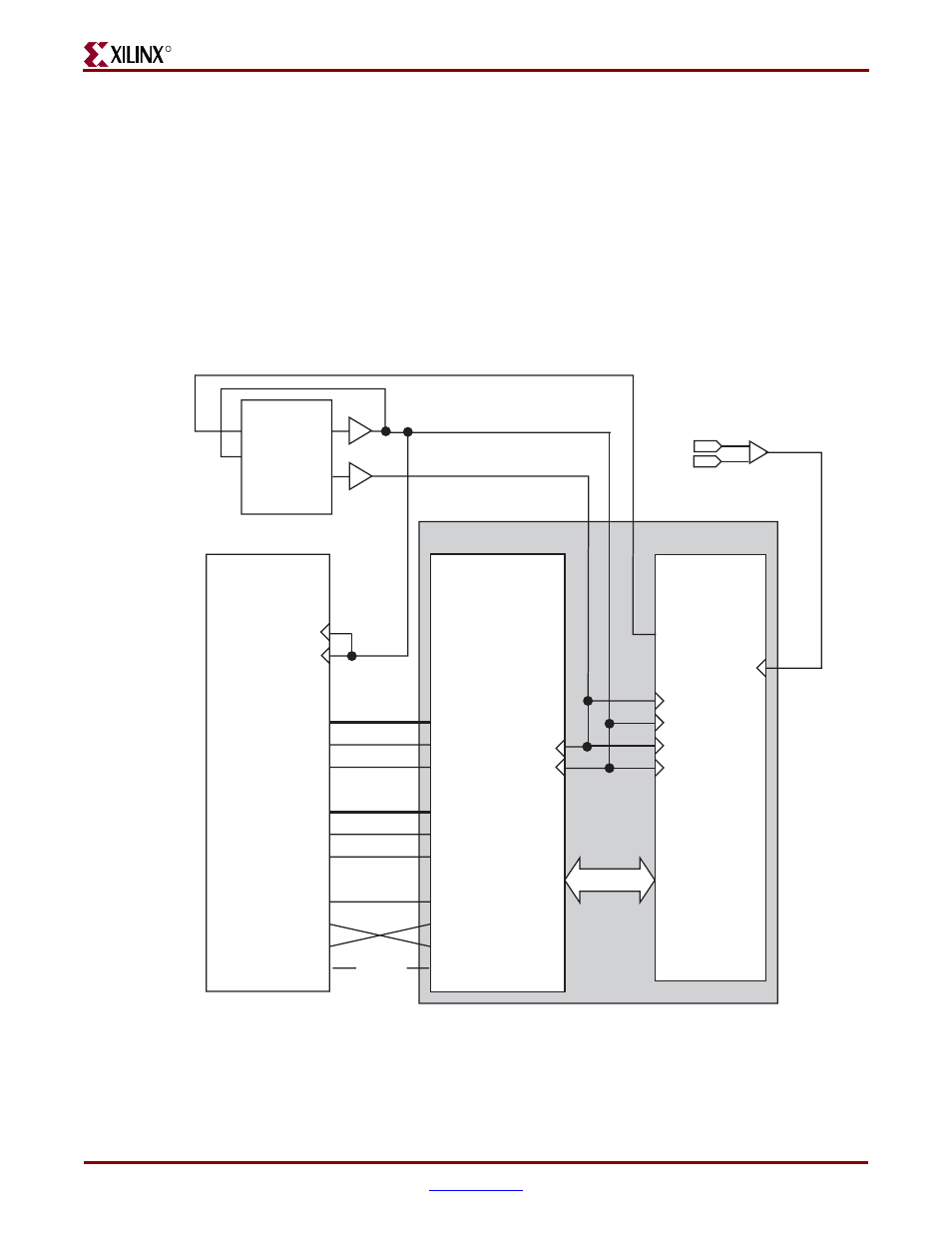

Due to the embedded Receiver Elastic Buffer in the Ethernet 1000BASE-X PCS/PMA

or SGMII core, the entire GMII is synchronous to a single clock domain. For this

reason, userclk2 is used as the 125 MHz reference clock for both cores and the

transmitter and receiver logic of the GEMAC core now operate in the same clock

domain. This allows clock crossing constraints between the gtx_clk and

gmii_rx_clk

clock domains to be removed from the GEMAC UCF. See

for Critical Logic within the Core.”

Virtex-5 FXT Devices

illustrates the connections and clock management logic required to interface

the GEMAC core to the Ethernet 1000BASE-X PCS/PMA or SGMII core (when used in

1000BASE-X mode with PMA using the device-specific RocketIO transceiver).

Figure 11-4:

1-Gigabit Ethernet MAC Extended to Include 1000BASE-X PCS and PMA

using the RocketIO transceiver

1-Gigabit Ethernet

MAC

LogiCORE

gmii_rx_clk

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

gtx_clk

mdc

mdio_in

mdio_out

mdio_tri

Ethernet 1000BASE-X

PCS/PMA or SGMII

LogiCORE

gmii_rxd[7:0]

gmii_rx_dv

gmii_rx_er

gmii_txd[7:0]

gmii_tx_en

gmii_tx_er

mdc

mdio_in

mdio_out

mdio_tri

Virtex-5

GTX

RocketIO

no

connection

userclk

userclk2

RocketIO I/F

CLKIN

userclk2 (125MHz)

TXUSRCLK0

TXUSRCLK20

RXUSRCLK0

RXUSRCLK20

REFCLKOUT

component_name_block

(Block Level from example design)

clkin

(125MHz)

IBUFGDS

IPAD

brefclkp

IPAD

brefclkn

DCM

CLKIN

CLK0

FB

BUFG

CLKDV

BUFG

userclk (62.5MHz)