4 priority allocation, Product preview – Texas Instruments TMS320C6454 User Manual

Page 76

www.ti.com

PRODUCT PREVIEW

4.4 Priority Allocation

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

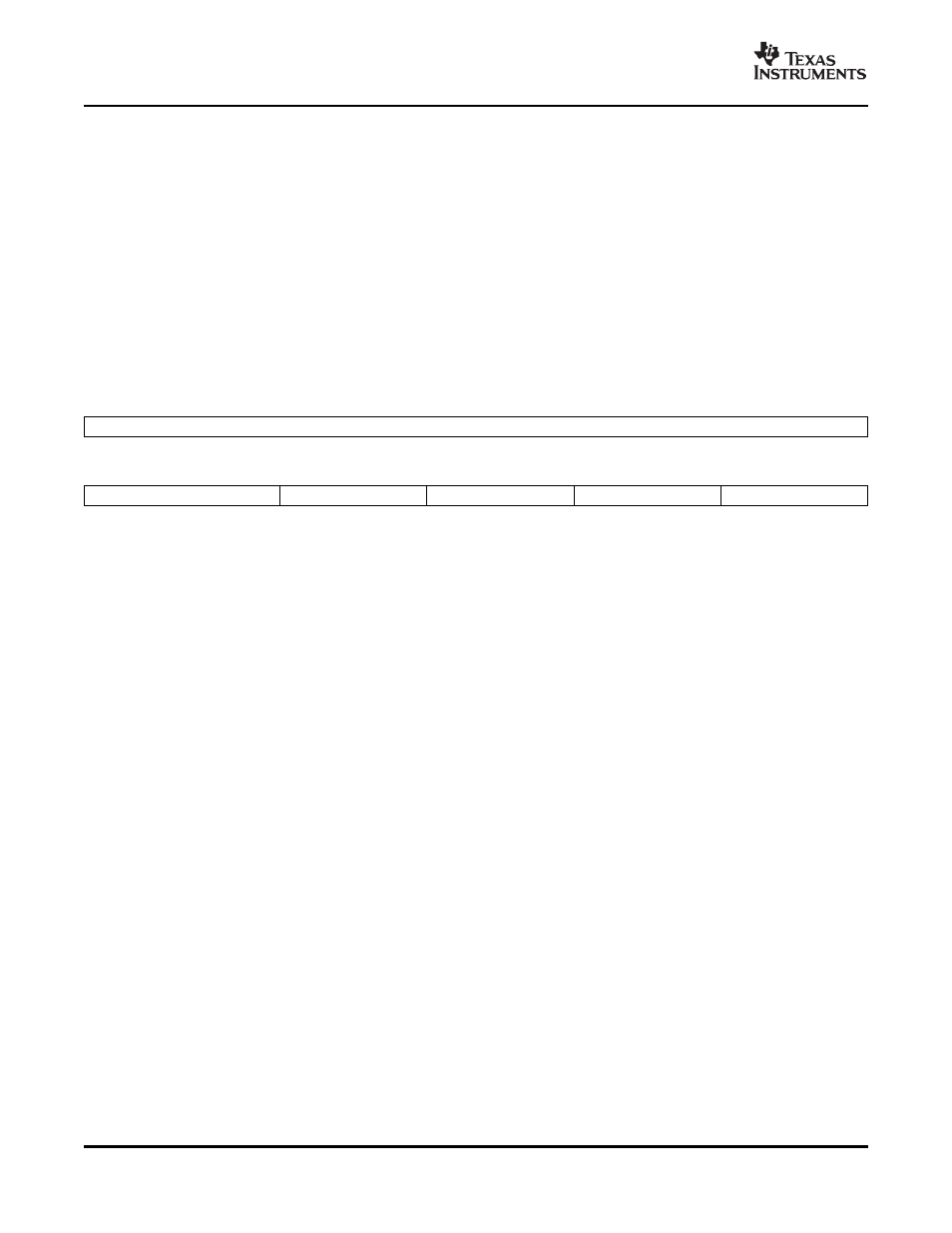

On the C6454 device, each of the masters (excluding the C64x+ Megamodule) are assigned a priority via

the Priority Allocation Register (PRI_ALLOC), see

. The priority is enforced when several

masters in the system are vying for the same endpoint. A value of 000b has the highest priority, while

111b has the lowest priority.

Note that the configuration SCR port on the data SCR is considered a single endpoint meaning priority will

be enforced when multiple masters try to access the configuration SCR. Priority is also enforced on the

configuration SCR side when a master (through the data SCR) tries to access the same endpoint as the

C64x+ Megamodule.

Other Master peripherals are not present in the PRI_ALLOC register as they have their own registers to

program their priorities. For more information on the default priority values in these peripheral registers,

see the device-compatible peripheral reference guides. TI recommends that these priority registers be

reprogrammed upon initial use.

31

16

Reserved

R-0000 0000 0000 0000

15

12

11

9

8

6

5

3

2

0

Reserved

Reserved

Reserved

HOST

EMAC

R-000 0

R/W-001

R-0

R/W-010

R/W-001

LEGEND: R/W = Read/Write; R = Read only; -n = value at reset

Figure 4-3. Priority Allocation Register (PRI_ALLOC)

System Interconnect

76