Product preview – Texas Instruments TMS320C6454 User Manual

Page 179

www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

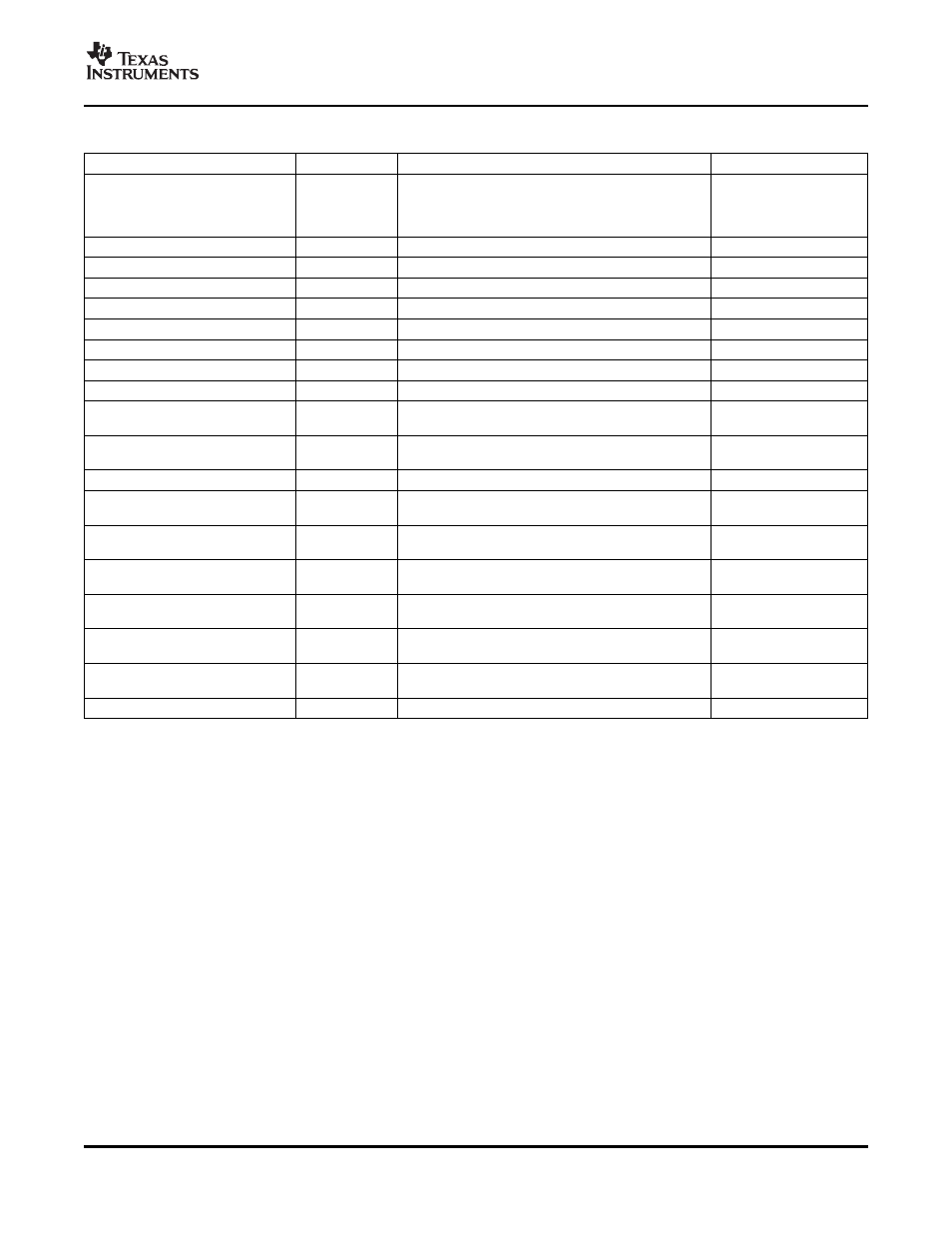

Table 7-58. McBSP 1 Registers

HEX ADDRESS RANGE

ACRONYM

REGISTER NAME

COMMENTS

The CPU and EDMA

controller can only read

0290 0000

DRR1

McBSP1 Data Receive Register via Configuration Bus

this register; they cannot

write to it.

3400 0000

DRR1

McBSP1 Data Receive Register via EDMA bus

0290 0004

DXR1

McBSP1 Data Transmit Register via configuration bus

3400 0010

DXR1

McBSP1 Data Transmit Register via EDMA bus

0290 0008

SPCR1

McBSP1 serial port control register

0290 000C

RCR1

McBSP1 Receive Control Register

0290 0010

XCR1

McBSP1 Transmit Control Register

0290 0014

SRGR1

McBSP1 sample rate generator register

0290 0018

MCR1

McBSP1 multichannel control register

McBSP1 Enhanced Receive Channel Enable

0290 001C

RCERE01

Register 0 Partition A/B

McBSP1 Enhanced Transmit Channel Enable

0290 0020

XCERE01

Register 0 Partition A/B

0290 0024

PCR1

McBSP1 Pin Control Register

McBSP1 Enhanced Receive Channel Enable

0290 0028

RCERE11

Register 1 Partition C/D

McBSP1 Enhanced Transmit Channel Enable

0290 002C

XCERE11

Register 1 Partition C/D

McBSP1 Enhanced Receive Channel Enable

0290 0030

RCERE21

Register 2 Partition E/F

McBSP1 Enhanced Transmit Channel Enable

0290 0034

XCERE21

Register 2 Partition E/F

McBSP1 Enhanced Receive Channel Enable

0290 0038

RCERE31

Register 3 Partition G/H

McBSP1 Enhanced Transmit Channel Enable

0290 003C

XCERE31

Register 3 Partition G/H

0290 0040 - 0293 FFFF

-

Reserved

C64x+ Peripheral Information and Electrical Specifications

179