17 general-purpose input/output (gpio), 1 gpio device-specific information, 2 gpio peripheral register description(s) – Texas Instruments TMS320C6454 User Manual

Page 214: Product preview

www.ti.com

PRODUCT PREVIEW

7.17 General-Purpose Input/Output (GPIO)

7.17.1 GPIO Device-Specific Information

7.17.2 GPIO Peripheral Register Description(s)

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

On the C6454 the GPIO peripheral pins GP[15:8] and GP[3:0] are muxed with the PCI and McBSP1

peripheral pins and the SYSCLK4 signal. For more detailed information on device/peripheral configuration

and the C6454 device pin muxing, see

, Device Configuration.

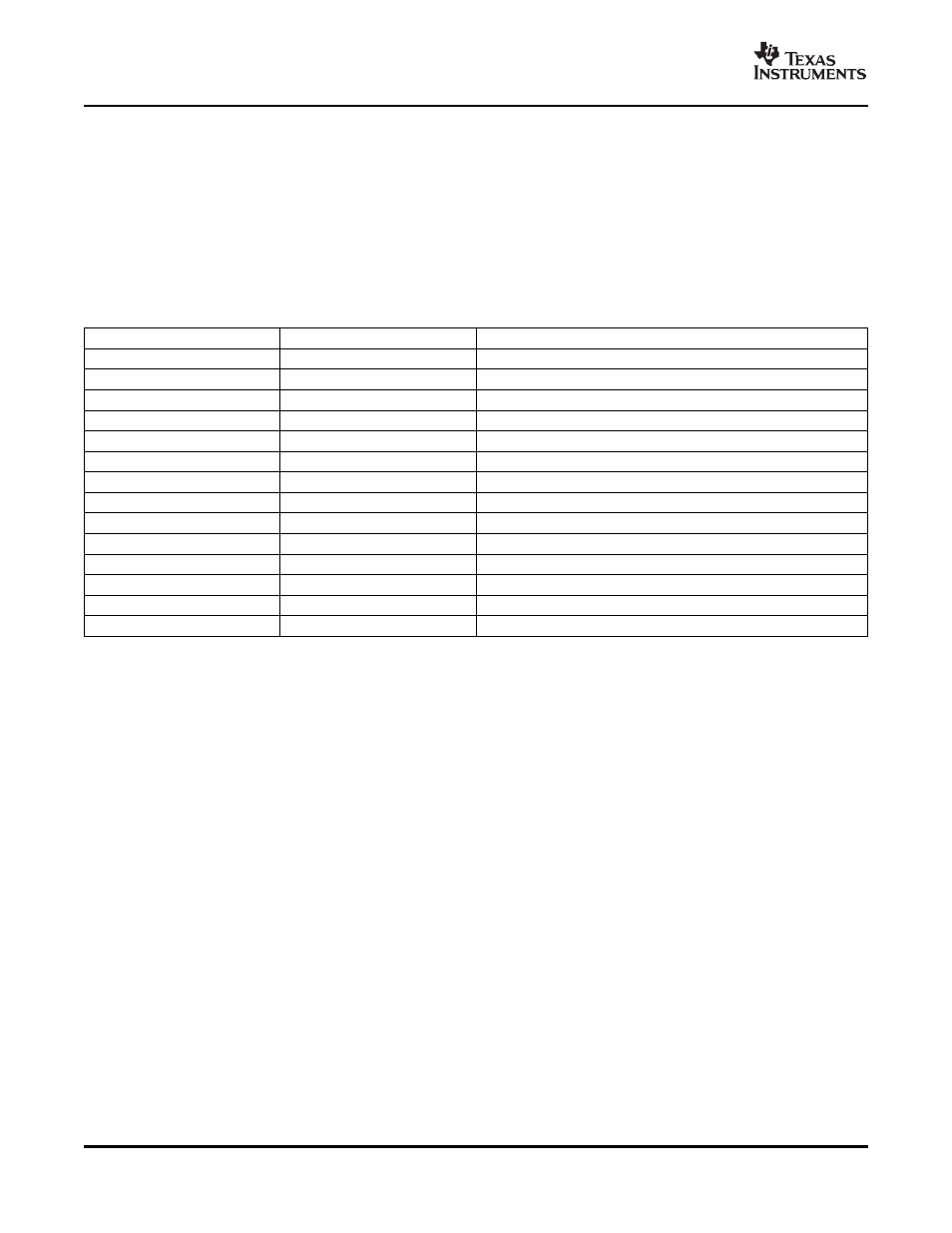

Table 7-102. GPIO Registers

HEX ADDRESS RANGE

ACRONYM

REGISTER NAME

02B0 0008

BINTEN

GPIO interrupt per bank enable register

02B0 000C

-

Reserved

02B0 0010

DIR

GPIO Direction Register

02B0 0014

OUT_DATA

GPIO Output Data register

02B0 0018

SET_DATA

GPIO Set Data register

02B0 001C

CLR_DATA

GPIO Clear Data Register

02B0 0020

IN_DATA

GPIO Input Data Register

02B0 0024

SET_RIS_TRIG

GPIO Set Rising Edge Interrupt Register

02B0 0028

CLR_RIS_TRIG

GPIO Clear Rising Edge Interrupt Register

02B0 002C

SET_FAL_TRIG

GPIO Set Falling Edge Interrupt Register

02B0 0030

CLR_FAL_TRIG

GPIO Clear Falling Edge Interrupt Register

02B0 008C

-

Reserved

02B0 0090 - 02B0 00FF

-

Reserved

02B0 0100 - 02B0 3FFF

-

Reserved

C64x+ Peripheral Information and Electrical Specifications

214