Product preview – Texas Instruments TMS320C6454 User Manual

Page 28

www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

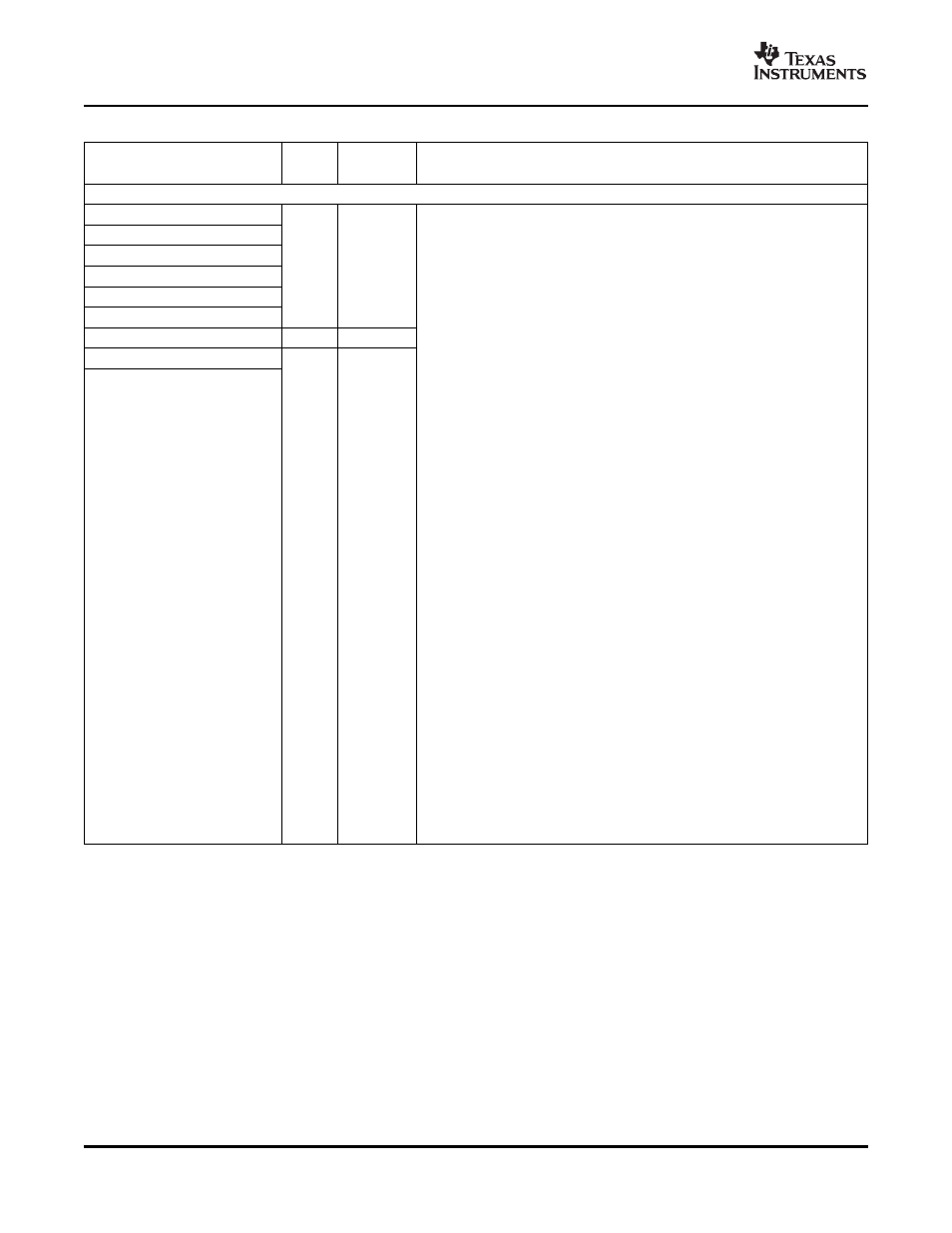

Table 2-3. Terminal Functions (continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAME

NO.

EMIFA (64-BIT) - ADDRESS

AEA19/BOOTMODE3

N25

EMIFA external address (word address) (O/Z)

Controls initialization of the DSP modes at reset (I) via pullup/pulldown resistors

AEA18/BOOTMODE2

L26

[For more detailed information, see

, Device Configuration.]

AEA17/BOOTMODE1

L25

Note: If a configuration pin must be routed out from the device, the internal

O/Z

IPD

pullup/pulldown (IPU/IPD) resistor should not be relied upon; TI recommends

AEA16/BOOTMODE0

P26

the use of an external pullup/pulldown resistor.

AEA15/AECLKIN_SEL

P27

•

Boot mode - device boot mode configurations (BOOTMODE[3:0]) [Note:

AEA14/HPI_WIDTH

R25

the peripheral must be enabled to use the particular boot mode.]

AEA13/LENDIAN

R27

O/Z

IPU

AEA[19:16]:

0000 - No boot (default mode)

AEA12

R28

0001 - Host boot (HPI)

0010 -Reserved

0011 - Reserved

0100 - EMIFA 8-bit ROM boot

0101 - Master I2C boot

0110 - Slave I2C boot

0111 - Host boot (PCI)

1000 thru 1111 - Reserved

For more detailed information on the boot modes, see

, Boot

Sequence.

CFGGP[2:0] pins must be set to 000b during reset for proper operation of

the PCI boot mode.

•

EMIFA input clock source select

Clock mode select for EMIFA (AECLKIN_SEL)

AEA15:

0 - AECLKIN (default mode)

O/Z

IPD

1 - SYSCLK4 (CPU/x) Clock Rate. The SYSCLK4 clock rate is software

AEA11

T25

selectable via the Software PLL1 Controller. By default, SYSCLK4 is

selected as CPU/8 clock rate.

•

HPI peripheral bus width (HPI_WIDTH) select

[Applies only when HPI is enabled; PCI_EN pin = 0]

AEA14:

0 - HPI operates as an HPI16 (default). (HPI bus is 16 bits wide. HD[15:0]

pins are used and the remaining HD[31:16] pins are reserved pins in the

Hi-Z state.)

1 - HPI operates as an HPI32.

•

Device Endian mode (LENDIAN)

AEA13:

0 - System operates in Big Endian mode

1 - System operates in Little Endian mode(default)

Note: For proper C6454 device operation, the AEA12 and AEA11 pins must

be externally pulled down with a 1-k

Ω

resistor at device reset.

Device Overview

28