Product preview – Texas Instruments TMS320C6454 User Manual

Page 143

www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

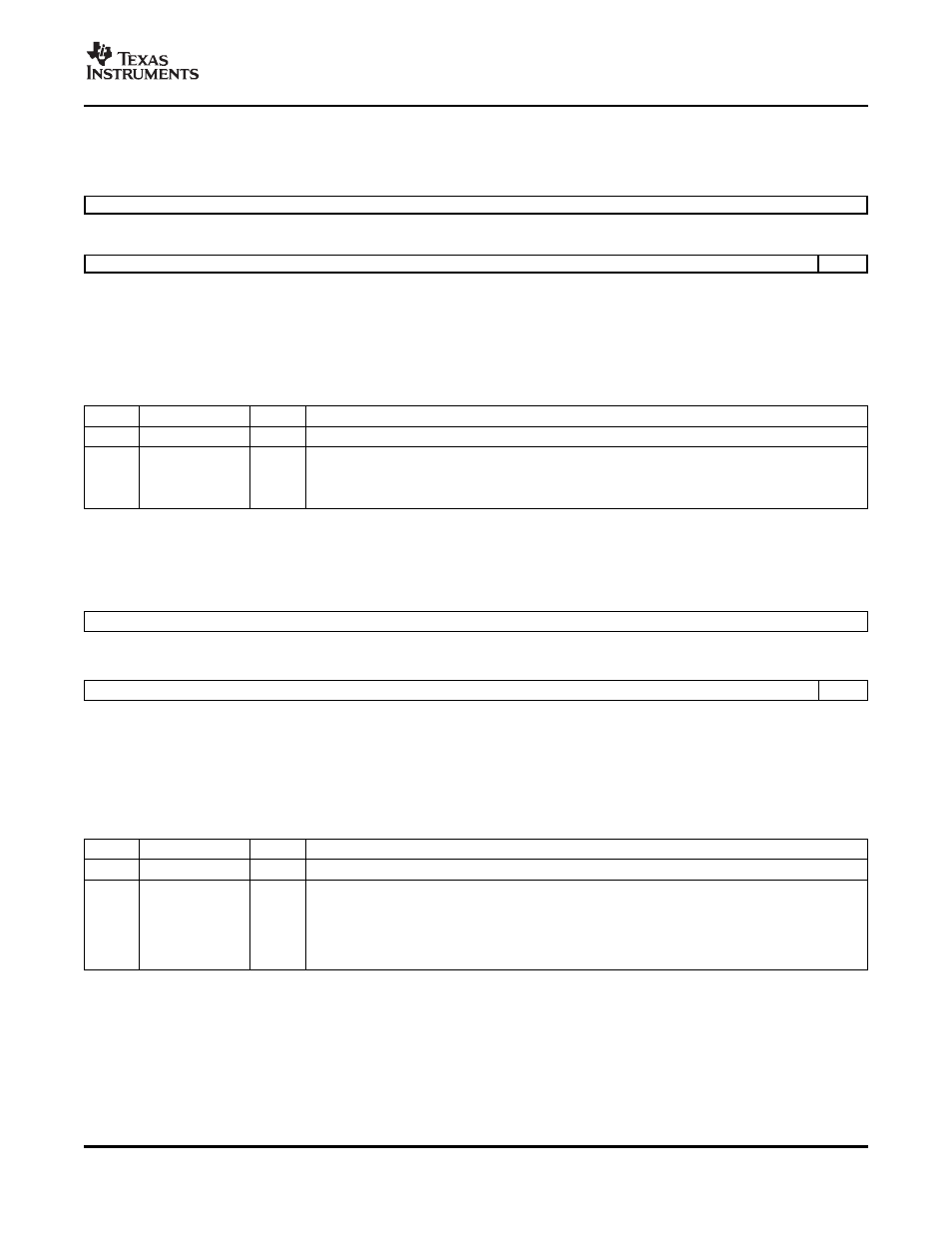

7.8.3.3 PLL Controller Status Register

The PLL controller status register (PLLSTAT) shows the PLL controller status. PLLSTAT is shown in

and described in

.

31

16

Reserved

R-0

15

1

0

Reserved

GOSTAT

R-0

R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Figure 7-26. PLL Controller Status Register (PLLSTAT) [Hex Address: 029C 013C]

Table 7-35. PLL Controller Status Register (PLLSTAT) Field Descriptions

Bit

Field

Value

Description

31:1

Reserved

0

Reserved. The reserved bit location is always read as 0. A value written to this field has no effect.

0

GOSTAT

GO operation status.

0

Go operation is not in progress. SYSCLK divide ratios are not being changed.

1

GO operation is in progress. SYSCLK divide ratios are being changed.

7.8.3.4 PLL Controller Clock Align Control Register

The PLL controller clock align control register (ALNCTL) is shown in

and described in

31

16

Reserved

R-0

15

1

0

Reserved

ALN1

R-0

R/W-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Figure 7-27. PLL Controller Clock Align Control Register (ALNCTL) [Hex Address: 029C 0140]

Table 7-36. PLL Controller Clock Align Control Register (ALNCTL) Field Descriptions

Bit

Field

Value

Description

31:1

Reserved

0

Reserved. The reserved bit location is always read as 0. A value written to this field has no effect.

0

ALN1

SYSCLK1 alignment. Do not change the default values of these fields.

0

Do not align SYSCLK1 during GO operation. If SYS1 in DCHANGE is set to 1, SYSCLK1 switches

to the new ratio immediately after the GOSET bit in PLLCMD is set.

1

Align SYSCLK1 when the GOSET bit in PLLCMD is set. The SYSCLK1 ratio is set to the ratio

programmed in the RATIO bit in PLLDIV1.

C64x+ Peripheral Information and Electrical Specifications

143