Product preview – Texas Instruments TMS320C6454 User Manual

Page 202

www.ti.com

PRODUCT PREVIEW

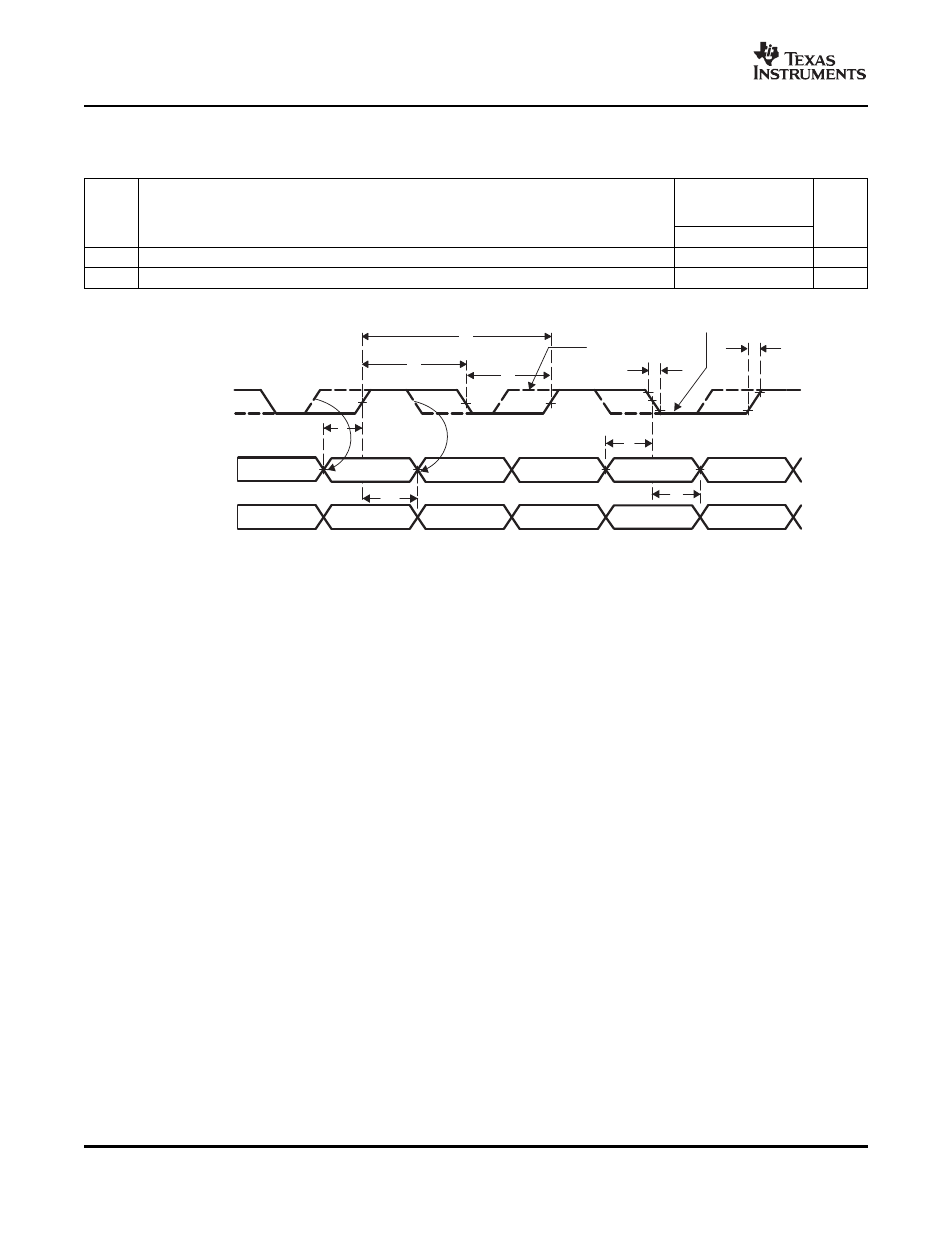

TXC (at DSP)

(B)

TXD[3:0]

(A)

TXCTL

(A)

5

6

1st Half-byte

TXERR

TXEN

2nd Half-byte

1

2

Internal TXC

TXC at DSP pins

4

4

2

3

1

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

Table 7-88. Switching Characteristics Over Recommended Operating Conditions for EMAC RGMII

Transmit

(1)

(see

-720

-850

NO.

PARAMETER

UNIT

-1000

MIN

MAX

5

t

su(TXD-TXCH)

Setup time, transmit selected signals valid before TXC (at DSP) high/low

1.2

ns

6

t

h(TXCH-TXD)

Hold time, transmit selected signals valid after TXC (at DSP) high/low

1.2

(1)

For RGMII, transmit selected signals include: TXD[3:0] and TXCTL.

A.

Data and control information is transmitted using both edges of the clocks. TXD[3:0] carries data bits 3-0 on the rising

edge of TXC and data bits 7-4 on the falling edge of TXC. Similarly, TX_CTL carries TXEN on rising edge of TXC and

TXERR of falling edge.

B.

TXC is delayed internally before being driven to the TXC pin.

Figure 7-70. EMAC Transmit Interface Timing [RGMII Operation]

(A)(B)

202

C64x+ Peripheral Information and Electrical Specifications