Product preview – Texas Instruments TMS320C6454 User Manual

Page 26

www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

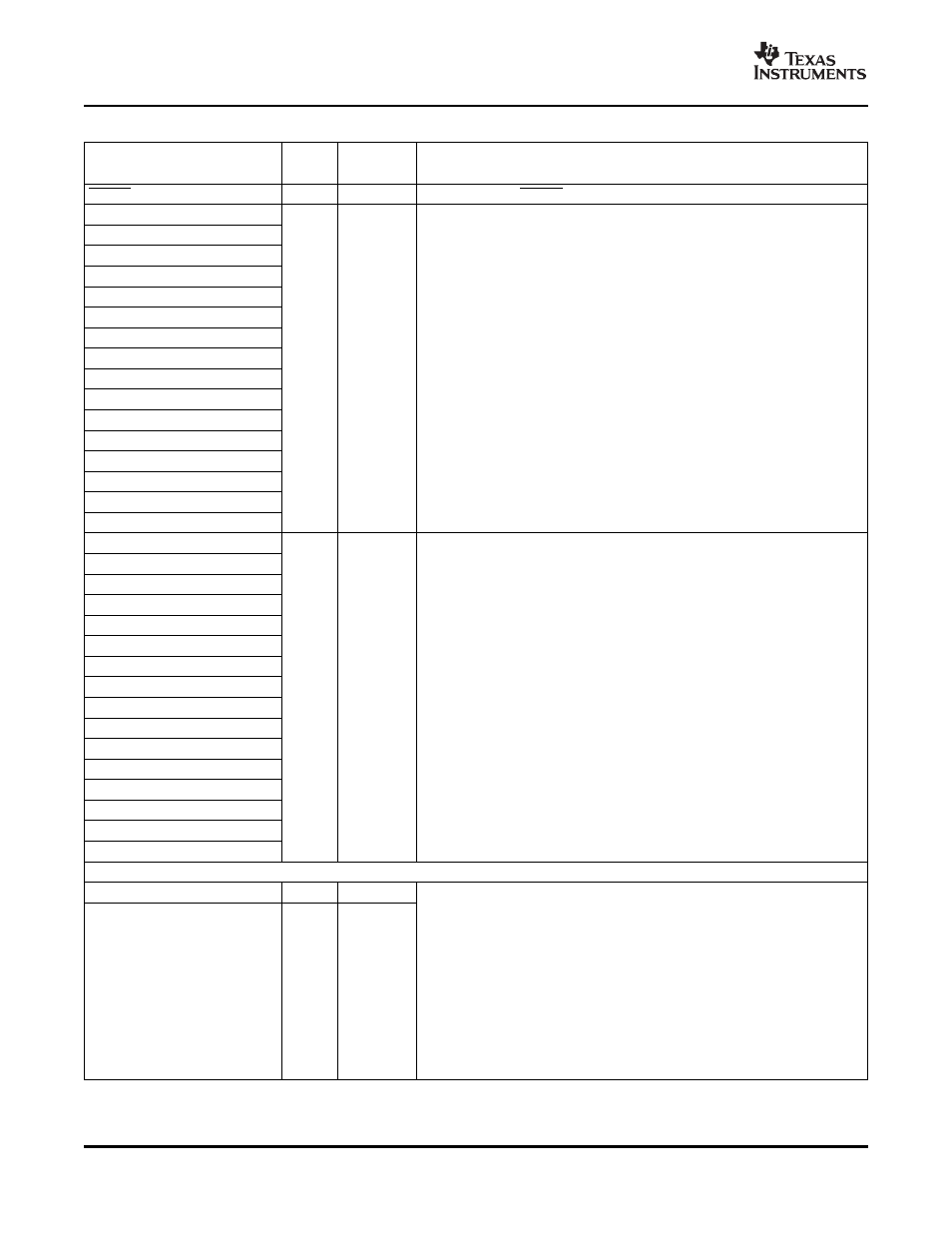

Table 2-3. Terminal Functions (continued)

SIGNAL

TYPE

(1)

IPD/IPU

(2)

DESCRIPTION

NAME

NO.

PTRDY

P4

I/O/Z

PCI target ready (PRTDY) (I/O/Z). By default, this pin has no function.

HD31/AD31

AA3

HD30/AD30

AA5

HD29/AD29

AC4

HD28/AD28

AA4

HD27/AD27

AC5

HD26/AD26

Y1

HD25/AD25

AD2

HD24/AD24

W1

Host-port data [31:16] pin (I/O/Z) [default] or PCI data-address bus [31:16]

I/O/Z

(I/O/Z)

HD23/AD23

AC3

HD22/AD22

AE1

HD21/AD21

AD1

HD20/AD20

W2

HD19/AD19

AC1

HD18/AD18

Y2

HD17/AD17

AB1

HD16/AD16

Y3

HD15/AD15

AB2

HD14/AD14

W4

HD13/AD13

AC2

HD12/AD12

V4

HD11/AD11

AF3

HD10/AD10

AE3

HD9/AD9

AB3

HD8/AD8

W5

I/O/Z

Host-port data [15:0] pin (I/O/Z) [default] or PCI data-address bus [15:0] (I/O/Z)

HD7/AD7

AB4

HD6/AD6

Y4

HD5/AD5

AD3

HD4/AD4

Y5

HD3/AD3

AD4

HD2/AD2

W6

HD1/AD1

AB5

HD0/AD0

AE2

EMIFA (64-BIT) - CONTROL SIGNALS COMMON TO ALL TYPES OF MEMORY

ABA1/EMIFA_EN

V25

O/Z

IPD

EMIFA bank address control (ABA[1:0])

•

Active-low bank selects for the 64-bit EMIFA.

When interfacing to 16-bit Asynchronous devices, ABA1 carries bit 1 of the

byte address.

For an 8-bit Asynchronous interface, ABA[1:0] are used to carry bits 1 and

0 of the byte address

DDR2 Memory Controller enable (DDR2_EN) [ABA0]

ABA0/DDR2_EN

V26

O/Z

IPD

0 - DDR2 Memory Controller peripheral pins are disabled (default)

1 - DDR2 Memory Controller peripheral pins are enabled

EMIFA enable (EMIFA_EN) [ABA1]

0 - EMIFA peripheral pins are disabled (default)

1 - EMIFA peripheral pins are enabled

Device Overview

26