Table 7-70, Product preview – Texas Instruments TMS320C6454 User Manual

Page 189

www.ti.com

PRODUCT PREVIEW

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

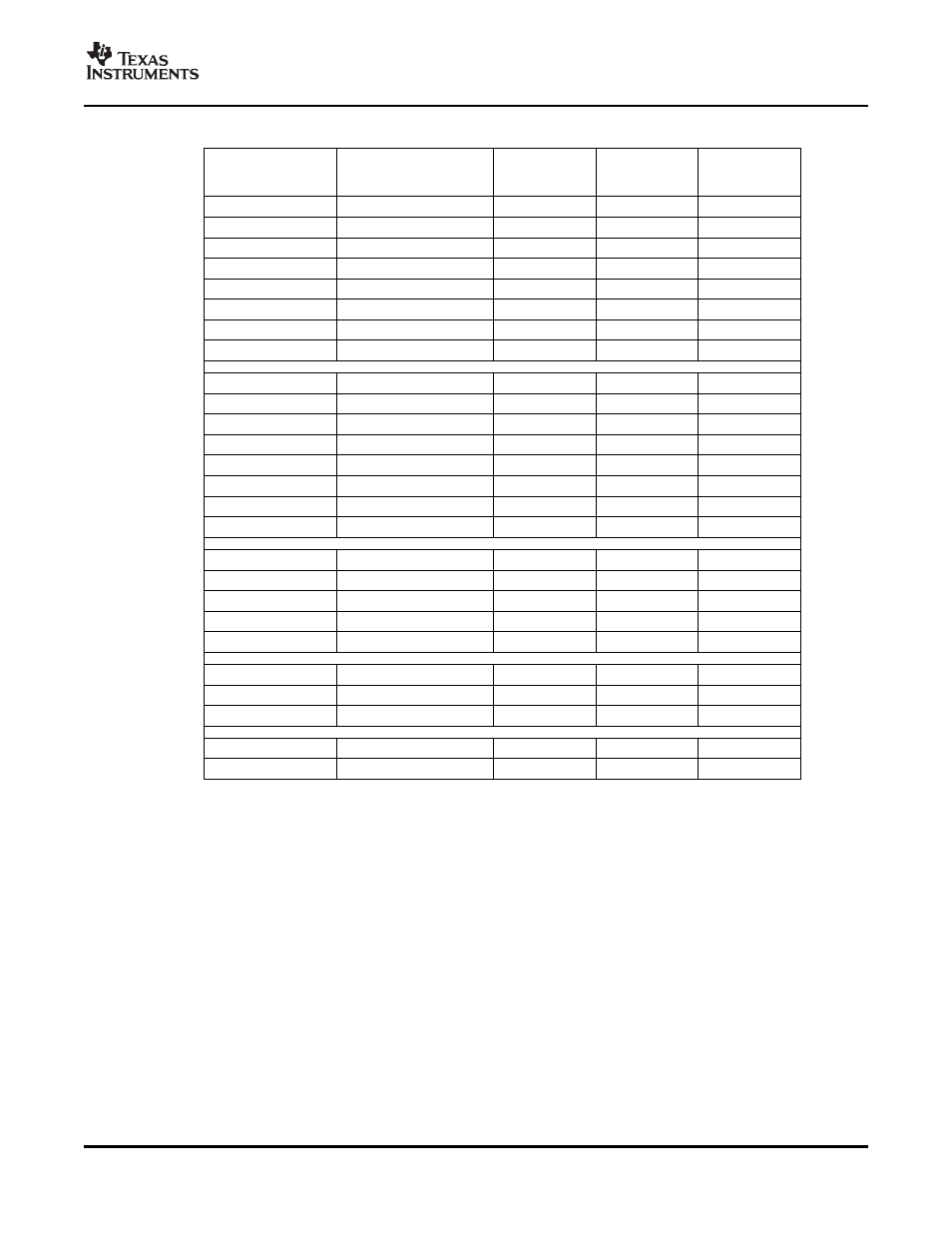

Table 7-70. EMAC/MDIO Multiplexed Pins (MII, RMII, and GMII Modes)

BALL NUMBER

DEVICE PIN NAME

MII

RMII

GMII

(MAC_SEL =

(MAC_SEL =

(MAC_SEL =

00b)

01b)

10b)

J2

MRXD0/RMRXD0

MRXD0

RMRXD0

MRXD0

H3

MRXD1/RMRXD1

MRXD1

RMRXD1

MRXD1

J1

MRXD2

MRXD2

MRXD2

J3

MRXD3

MRXD3

MRXD3

L1

MRXD4

MRXD4

L2

MRXD5

MRXD5

H2

MRXD6

MRXD6

M2

MRXD7

MRXD7

M1

MTXD0/RMTXD0

MTXD0

RMTXD0

MTXD0

L4

MTXD1/RMTXD1

MTXD1

RMTXD1

MTXD1

M4

MTXD2

MTXD2

MTXD2

K4

MTXD3

MTXD3

MTXD3

L3

MTXD4

MTXD4

L5

MTXD5

MTXD5

M3

MTXD6

MTXD6

N5

MTXD7

MTXD7

H4

MRXER/RMRXER

MRXER

RMRXER

MRXER

H5

MRXDV

MRXDV

MRXDV

J5

MTXEN/RMTXEN

MTXEN

RMTXEN

MTXEN

J4

MCRS/RMCRSDV

MCRS

RMCRSDV

MCRS

K3

MCOL

MCOL

MCOL

K5

GMTCLK

GMTCLK

H1

MRCLK

MRCLK

MRCLK

N4

MTCLK/REFCLK

MTCLK

RMREFCLK

MTCLK

N3

GMDIO

MDIO

MDIO

MDIO

M5

GMDCLK

MDCLK

MDCLK

MDCLK

Using the RMII Mode of the EMAC

The Ethernet Media Access Controller (EMAC) contains logic that allows it to communicate using the

Reduced Media Independent Interface (RMII) protocol. This logic must be taken out of reset before being

used. To use the RMII mode of the EMAC follow these steps:

1. Enable the EMAC/MDIO through the Device State Control Registers.

–

Unlock the PERCFG0 register by writing 0x0F0A 0B00 to the PERLOCK register.

–

Set bit 4 in the PERCFG0 register within 16 SYSCLK3 clock cycles to enable the EMAC/MDIO.

–

Poll the PERSTAT0 register to verify state change.

2. Initialize the EMAC/MDIO as needed.

3. Release the RMII logic from reset by clearing the RMII_RST bit of the EMAC Configuration Register

(see

As described in the previous section, the RMII mode of the EMAC must be selected by setting

MACSEL[1:0] = 01b at device reset.

C64x+ Peripheral Information and Electrical Specifications

189