3 peripheral configuration register 1 description, Product preview – Texas Instruments TMS320C6454 User Manual

Page 59

www.ti.com

PRODUCT PREVIEW

3.4.3

Peripheral Configuration Register 1 Description

TMS320C6454

Fixed-Point Digital Signal Processor

SPRS311A – APRIL 2006 – REVISED DECEMBER 2006

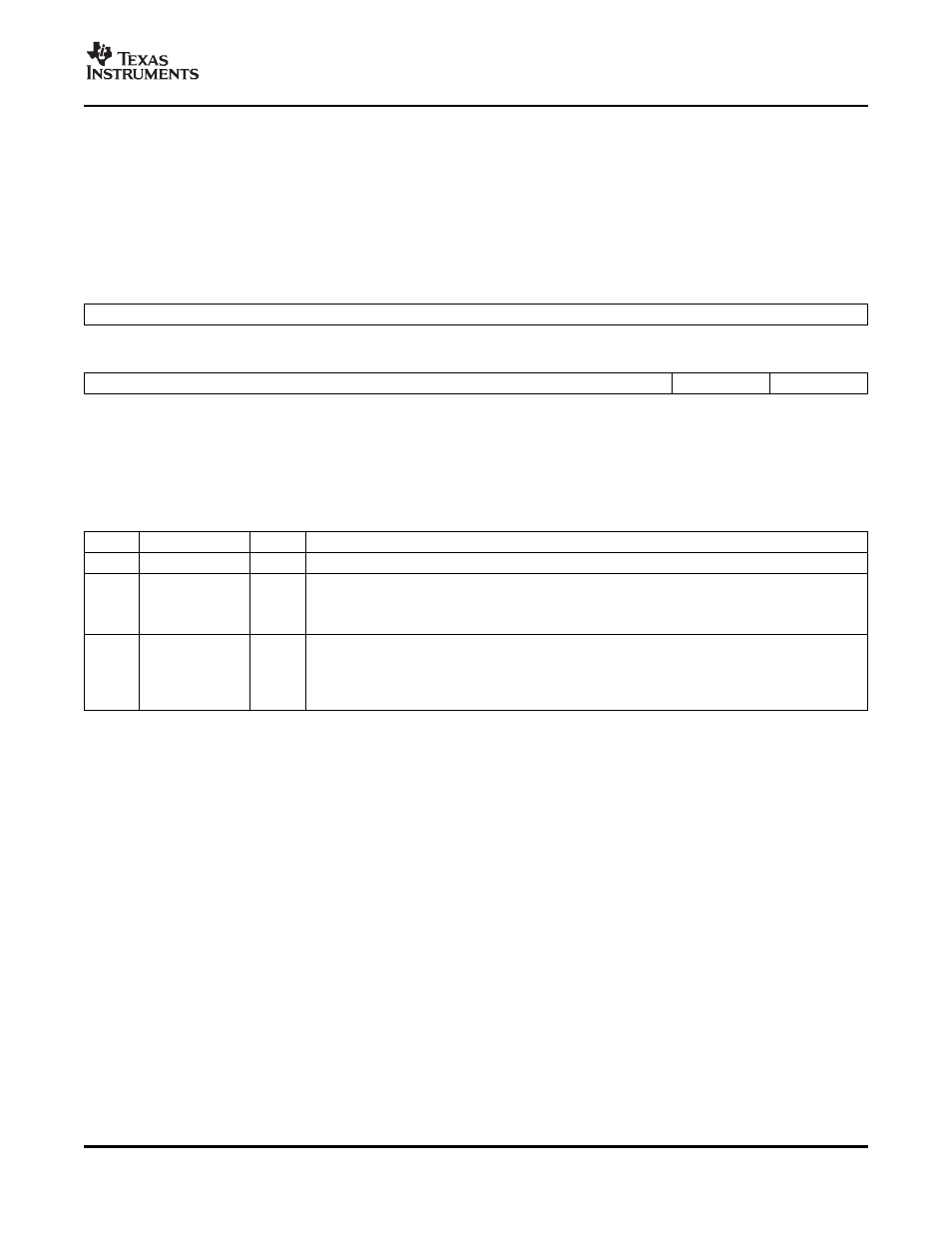

The Peripheral Configuration Register (PERCFG1) is used to enable the EMIFA and DDR2 Memory

Controller. EMIFA and the DDR2 Memory Controller do not have corresponding status bits in the

Peripheral Status Registers. The EMIFA and DDR2 Memory Controller peripherals can be used within 16

SYSCLK3 cycles after EMIFACTL and DDR2CTL are set to 1. Once EMIFACTL and DDR2CTL are set to

1, they cannot be set to 0. Note that if the DDR2 Memory Controller and EMIFA are disabled at reset

through the device configuration pins (DDR2.EN[ABA0] and EMIFA[ABA1]), they cannot be enabled

through the PERCFG1 register.

31

8

Reserved

R-0x00

7

2

1

0

Reserved

DDR2CTL

EMIFACTL

R-0x00

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Figure 3-5. Peripheral Configuration Register 1 (PERCFG1) - 0x02AC 002C

Table 3-8. Peripheral Configuration Register 1 (PERCFG1) Field Descriptions

Bit

Field

Value

Description

31:2

Reserved

Reserved.

1

DDR2CTL

Mode Control for DDR2 Memory Controller. Once this bit is set to 1, it cannot be changed to 0.

0

Set DDR2 to disabled

1

Set DDR2 to enabled

0

EMIFACTL

Mode control for EMIFA. Once this bit is set to 1, it cannot be changed to 0. This bit defaults to 1 if

EMIFA 8-bit ROM boot is used (BOOTMODE[3:0] = 0100b).

0

Set EMIFA to disabled

1

Set EMIFA to enabled

Device Configuration

59