2 the l2 cache – IBM RS/6000 User Manual

Page 40

Up to 66 MHz bus clock

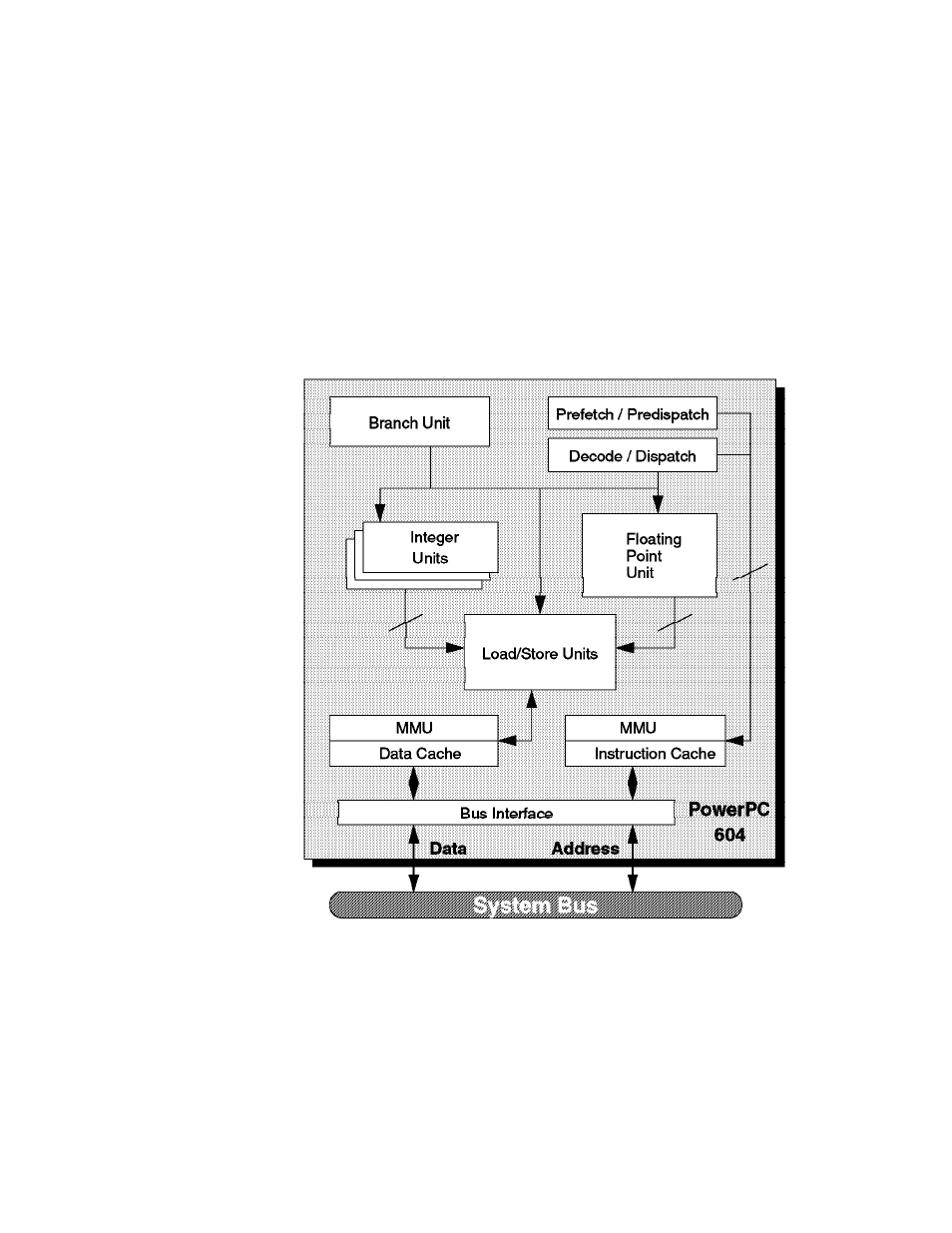

Superscalar design with integrated integer, floating-point and branch units

16 KB four-way set-associative instruction cache

16 KB four-way set-associative data cache

64-bit memory interface with 32-bit addressing

Virtual memory support for up to four petabytes (2

52

)

Real memory support for up to four gigabytes

Support for Big-Endian and Little-Endian modes

Nap power management mode

Figure 6. PowerPC 604 Microprocessor Logical Block Diagram

2.2.2 The L2 Cache

The L2 cache subsystem is directly attached to the processor bus which runs at 66

MHz. It is managed by a Write-Through Look-Aside controller which interfaces to

two Cache Tag RAM modules and eight synchronous Strip Cylindrical Random

Access Memory (SCRAM) modules to form a 512 KB L2 cache assembly.

16

Introduction to PCI-Based RS/6000 Servers

- I5 (59 pages)

- 2274 (183 pages)

- X3650 (18 pages)

- P5 570 (82 pages)

- 6E1 (40 pages)

- 704 (348 pages)

- SG24-4576-00 (235 pages)

- SCOD-3ZVQ5W (548 pages)

- LOTUS TEAM WORKPLACE 6.5.1 (17 pages)

- HANDBOOK 150 (286 pages)

- 6C4 (233 pages)

- 6059 (248 pages)

- 6644 (100 pages)

- 2283 (96 pages)

- 755 (47 pages)

- PANEL1173-841 (80 pages)

- G325-2585-02 (90 pages)

- BladeCenter T Type 8730 (180 pages)

- PC Server/Enterprise Racks 9QX (208 pages)

- X3620 M3 (19 pages)

- NETVISTA X40 6643 (120 pages)

- 440 (202 pages)

- xSeries 235 (66 pages)

- 47AE - 410168 (27 pages)

- TotalStorage DS6000 Series (406 pages)

- 310E (120 pages)

- NETVISTA 8319 (52 pages)

- A40P TYPE 6841 (148 pages)

- POWER 710 (45 pages)

- LCD PC (50 pages)

- 525 (33 pages)

- BladeCenter 8677 (104 pages)

- N2800e (82 pages)

- 6345 (214 pages)

- 2197 (208 pages)

- 4194 (84 pages)

- V7.2 (41 pages)

- SC34-6814-04 (953 pages)

- 6268 (53 pages)

- Enterprise Server H80 Series (230 pages)

- 6.00E+01 (42 pages)

- G544-5774-01 (56 pages)

- z/OS (88 pages)

- Aptiva 2140 (212 pages)

- GC23-7753-05 (56 pages)