AMETEK PLA-PLW Programming Manual User Manual

Page 45

41

and Operation Event registers to cause the following actions. This command is not channel specific, it

applies to the entire mainframe.

Ϯ When

a bit in the Operation NTR register is set to 1, then a 1-to-0 transition of the

corresponding bit in the Operation Condition register causes that bit in the

Operation Event register to be set.

Ϯ When

a bit of the Operation PTR register is set to 1, then a 0-to-1 transition of the

corresponding bit in the Operation Condition register causes that bit in the

Operation Event register to be set.

Ϯ If the same bits in both NTR and PTR registers are set to 1, then any transition of that

bit at the Operation Condition register sets the corresponding bit in the Operation

Event register.

Ϯ If the same bits in both NTR and PTR registers are set to 0, then no transition of that

bit at the Operation Condition register can set the corresponding bit in the Operation

Event register.

NOTE : Setting a bit in the PTR or NTR filter can of itself generate positive or negative events in the

corresponding Operation Event register.

Command Syntax

STATus:OPERation:NTR

STATus:OPERation:PTR

Parameters

0 to 32767 | MIN | MAX

Default Value

0

Query Syntax

STATus:OPERation:NTR?

STATus:OPERation:PTR?

Returned Parameters

Bit configuration of

Operation Enable register.

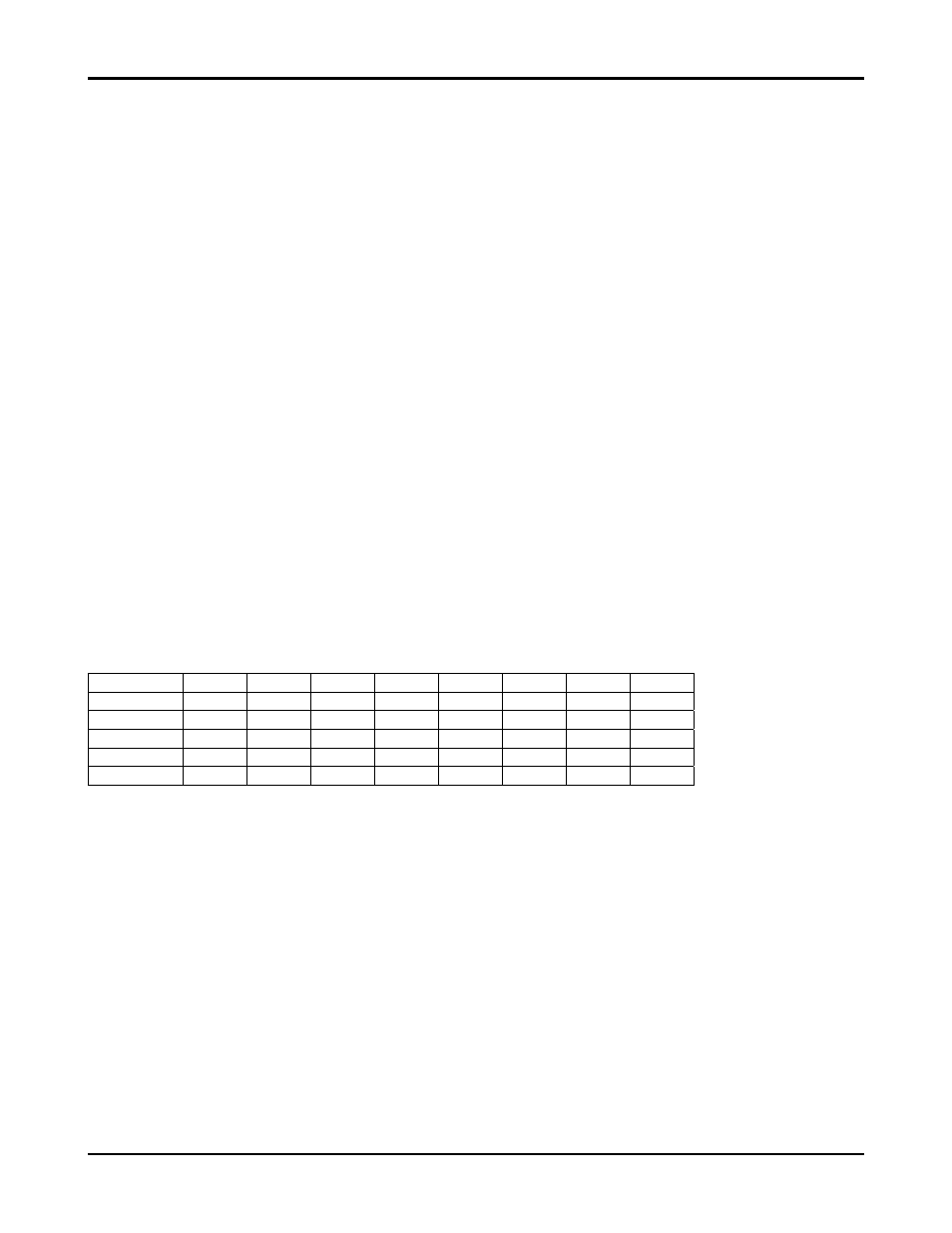

Bit

Position

7 6 5 4 3 2 1 0

Bit Name

RSF RC OT UP OP UC OC VF

Bit

Weight

218 64 32 16 8 4 2 1

Bit

Position

15 14 13 12 11 10 9 8

Bit Name LV OSC PS UV OV UNR RI UVL

Bit

Weight

32768

16384 8192 4096 2048 1024 512 256

VF

voltage fault has occurred

OC

over-current condition has occurred

UC

under-current condition has occurred

OP

over-power condition has occurred

UP

under-power condition has occurred

OT

over-temperature condition has occurred

RC

reverse-current condition has occurred

RSF

remote sense fault condition has occurred

UVL

under-voltage lock out condition has occurred

RI

Remote Inhibition condition has occurred

UNR

input is unregulated

OV

over-voltage condition has occurred

UV

under-voltage condition has occurred

PS

protection shutdown circuit has tripped

OSC oscillation protection condition has occurred

LV

low-voltage condition has occurred