Altera Stratix II GX PCI Express Development Board User Manual

Page 51

Altera Corporation

Reference Manual

2–41

August 2006

Stratix II GX PCI Express Development Board

Board Components & Interfaces

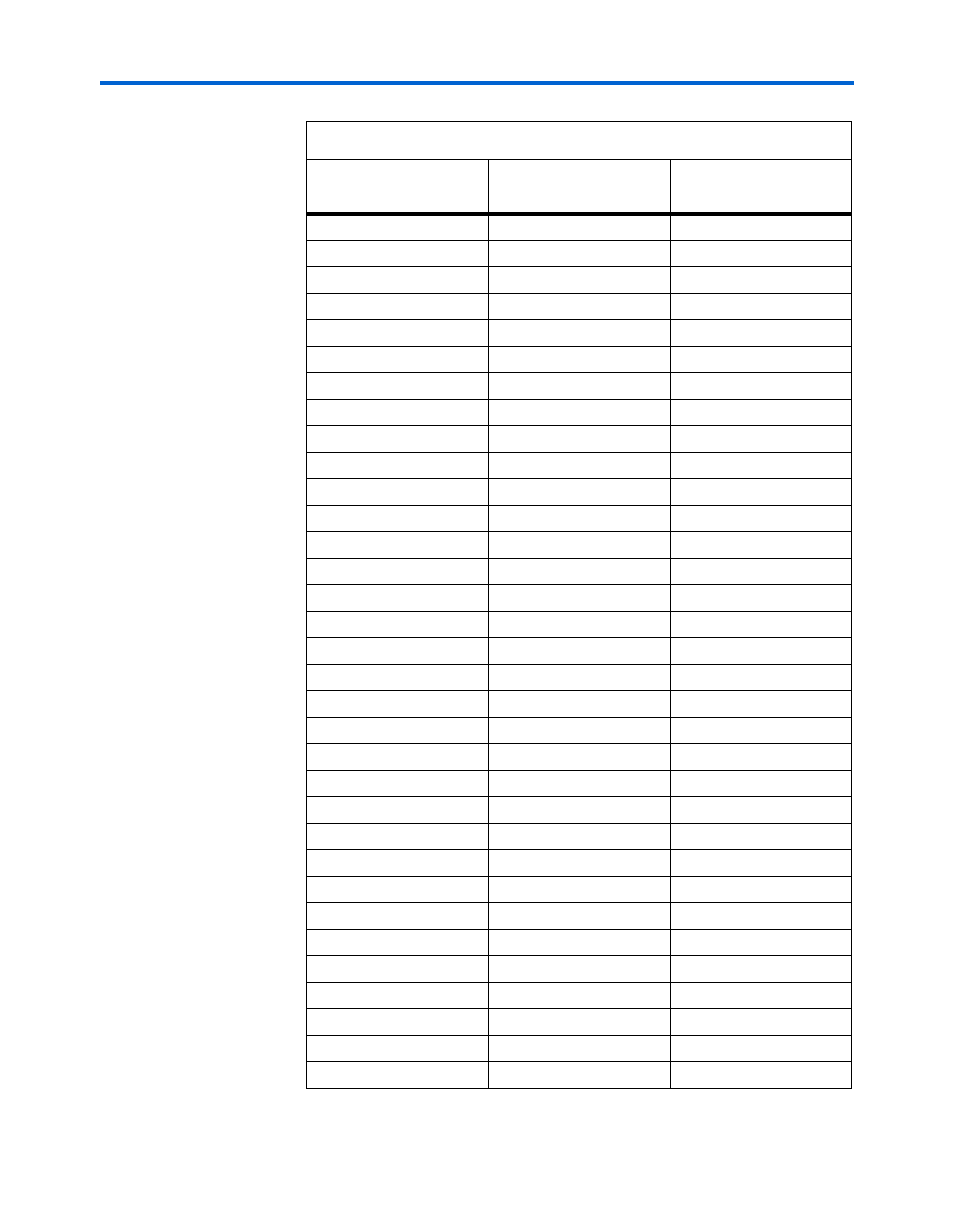

hsmb_sda

33

AD34

hsmb_tx_d_n[0]

49

AB33

hsmb_tx_d_n[1]

55

AA26

hsmb_tx_d_n[10]

115

AB31

hsmb_tx_d_n[11]

121

AC33

hsmb_tx_d_n[12]

127

AD31

hsmb_tx_d_n[13]

133

AD30

hsmb_tx_d_n[14]

139

AC27

hsmb_tx_d_n[15]

145

AE28

hsmb_tx_d_n[16]

151

AA25

hsmb_tx_d_n[2]

61

AB27

hsmb_tx_d_n[3]

67

AE33

hsmb_tx_d_n[4]

73

AB29

hsmb_tx_d_n[5]

79

AC25

hsmb_tx_d_n[6]

85

AD25

hsmb_tx_d_n[7]

91

AE26

hsmb_tx_d_n[8]

103

Y33

hsmb_tx_d_n[9]

109

AA31

hsmb_tx_d_p[0]

47

AA33

hsmb_tx_d_p[1]

53

Y27

hsmb_tx_d_p[10]

113

AB32

hsmb_tx_d_p[11]

119

AC34

hsmb_tx_d_p[12]

125

AD32

hsmb_tx_d_p[13]

131

AC30

hsmb_tx_d_p[14]

137

AB26

hsmb_tx_d_p[15]

143

AD27

hsmb_tx_d_p[16]

149

Y25

hsmb_tx_d_p[2]

59

AA27

hsmb_tx_d_p[3]

65

AD33

hsmb_tx_d_p[4]

71

AB30

hsmb_tx_d_p[5]

77

AB25

hsmb_tx_d_p[6]

83

AD26

hsmb_tx_d_p[7]

89

AE27

Table 2–28. HSMC B Connector Pin-Out

Schematic Signal Name

Samtec Pin Number

Stratix II GX

Pin Number

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- JESD204B IP (158 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Parallel Flash Loader IP (57 pages)

- Nios II C2H Compiler (138 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)