Featured device, Featured device -5 – Altera Stratix II GX PCI Express Development Board User Manual

Page 15

Altera Corporation

Reference Manual

2–5

August 2006

Stratix II GX PCI Express Development Board

Board Components & Interfaces

Featured

Device

The PCI Express Development Kit, Stratix II GX Edition features the FF1508

FPGA (U10) in a 1508-pin FineLine BGA

®

(FBGA) package.

Table 2–2

lists

some Stratix II GX device features.

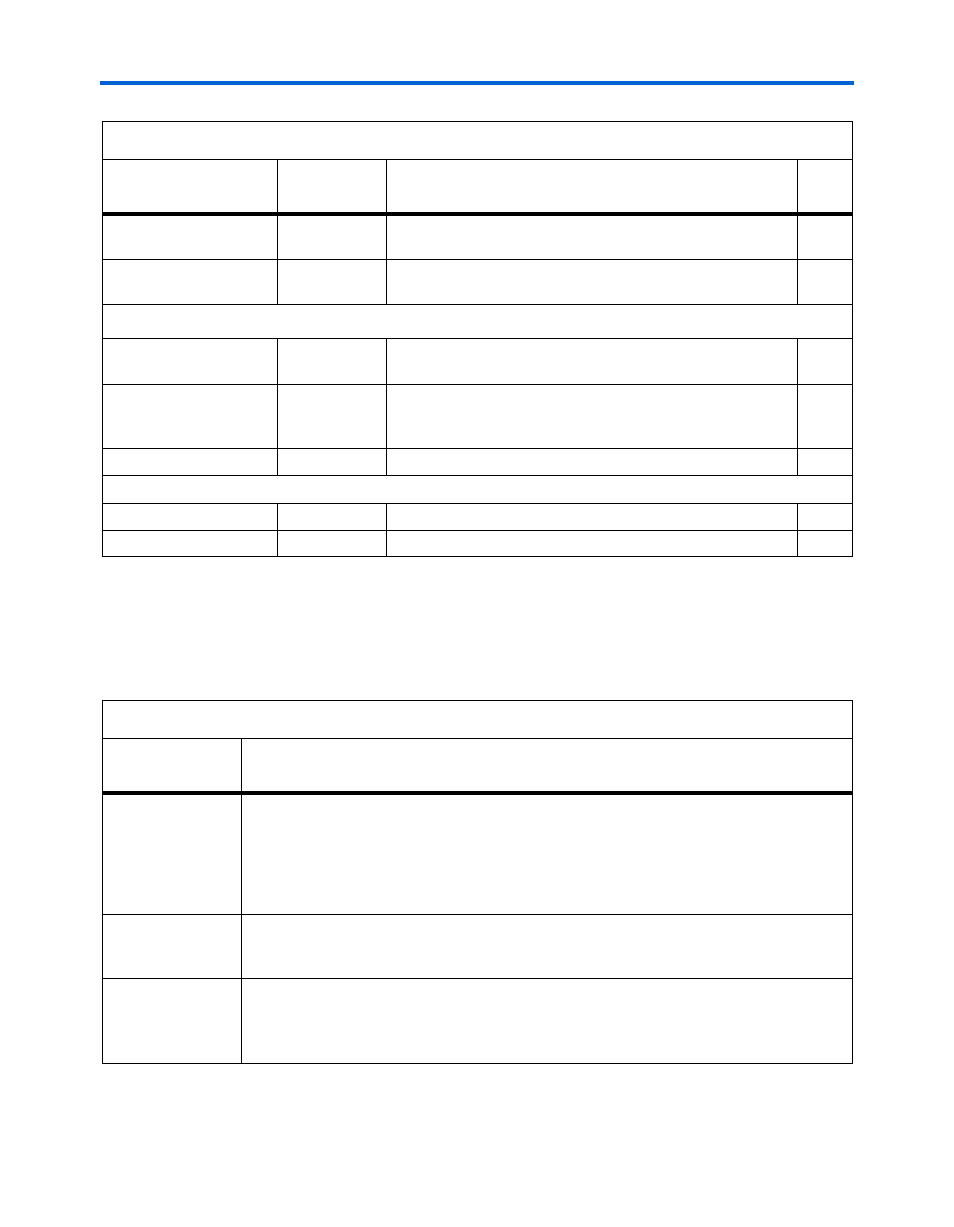

HSMC A

J1

High speed mezzanine connector allows for the connection

of HSMC daughter cards.

HSMC B

J2

High speed mezzanine connector allows for the connection

of HSMC daughter cards.

Memory

QDRII SRAM

U6

18 Mybtes (36 bits wide by 512 Kbytes deep) of QDRII

SRAM.

64 x 8 Mbyte DDR2

U2, U5, U8,

U11, U13

256 Mybtes (72 bits wide by 32 Mbytes deep) with error

correction coding (ECC) of double data rate (DDR2)

synchronous dynamic random access memory (SDRAM).

Flash

U3

512 Mbytes of flash memory.

Power

DC power jack

J3

DC input connector for the board.

Power switch

SW1

Switches the board’s power on or off.

Table 2–1. Stratix II GX PCIe Development Board Features

Component/

Interface

Board

Reference

Description

Page

Table 2–2. Stratix II GX Features

Architectural

Feature

Results

The Altera

®

third-generation

FPGA with

embedded

transceivers

●

Provides a robust design solution for the most popular high-speed serial interfaces

●

Provides optimum jitter performance across the entire operating range of 622 Mbps to

6.375 Gbps

●

Provides best-in class signal integrity performance

●

Offers enhanced transmit pre-emphasis technology, programmable receiver

equalization, and output voltage control

Innovative clock

management

system

●

Clock signals are automatically routed to the appropriate destination

●

Greatly simplifies high-speed board designs

●

Internal clock frequency of up to 500 MHz

Based on the

1.2-V, 90-nm

SRAM process

●

Provides up to 6.7 Mbits of on-chip TriMatrix

™

memory

●

Provides up to 63 DSP blocks for efficient implementation of high-performance filters

and other DSP functions

●

Supports a wide range of external memory interfaces