Altera SerialLite III Streaming MegaCore Function User Manual

Page 9

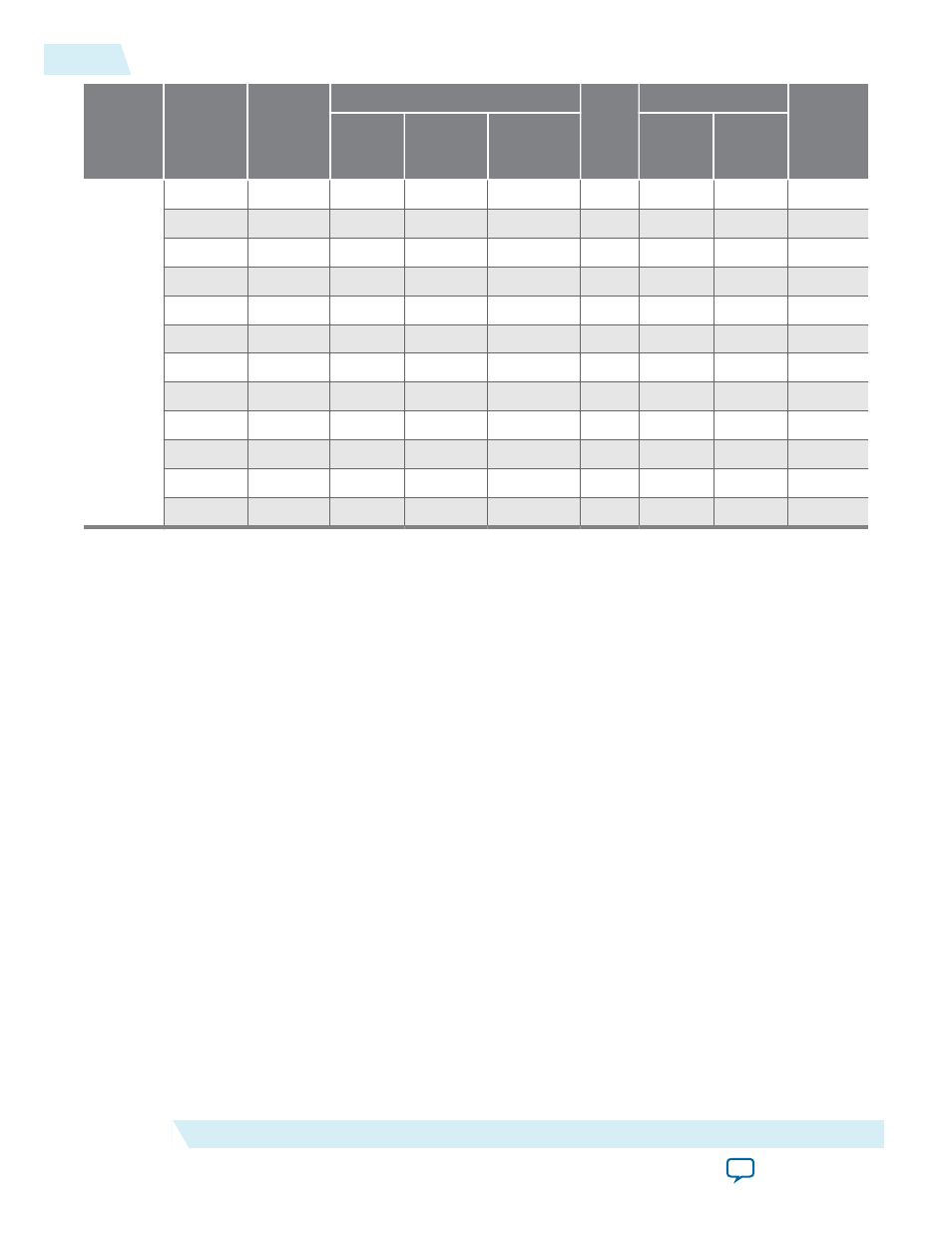

Device

Direction

Clocking

Mode

Parameters

ALMs

Logic Registers

M20K

Number

of Lanes

Per-Lane

Data Rate

(Mbps)

ECC

Primary Secondary

Stratix

V GX

and

Arria

V GZ

Source

Standard 24

10312.50 Disabled

6257

4511

142

48

Standard 24

10312.50 Enabled

7191

6636

459

72

Advanced 24

10312.50 Disabled

6265

4482

196

87

Advanced 24

10312.50 Enabled

8038

9013

761

121

Sink

Standard 24

10312.50 Disabled

5159

7962

267

48

Standard 24

10312.50 Enabled

3779

9761

802

72

Advanced 24

10312.50 Disabled

6058

7995

258

0

Advanced 24

10312.50 Enabled

5891

9789

905

72

Duplex

Standard 24

10312.50 Disabled

4680

11819

482

96

Standard 24

10312.50 Enabled

6419

15829

1249

144

Advanced 24

10312.50 Disabled

5582

11779

514

87

Advanced 24

10312.50 Enabled

7018

18393

1410

193

Related Information

More information about Quartus II resource utilization reporting.

2-4

Performance and Resource Utilization

UG-01126

2015.05.04

Altera Corporation

About the SerialLite III Streaming IP Core

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- JESD204B IP (158 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Parallel Flash Loader IP (57 pages)

- Nios II C2H Compiler (138 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)