Seriallite iii streaming duplex core, Seriallite iii streaming duplex core -9 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 33

SerialLite III Streaming Duplex Core

For Arria 10 devices, the duplex core is composed of source and sink cores interfaced with the Native

PHY IP core in Interlaken mode.

For Stratix V and Arria V GZ devices, the duplex core is composed of source and sink cores interfaced

with the Interlaken PHY IP in duplex mode.

Interlaken PHY IP Duplex Core or Native PHY IP Duplex Core - Interlaken Mode

For Arria 10 devices, this block is an instance of the Native PHY IP core configured for duplex Interlaken

operation. For lane rates from 15.625 to 17.4 Gbps, inclusive, the PMA width for Interlaken mode is 64

bits. For lane rates less than 15.625 Gbps, the PMA width is 40 bits.

For Stratix V and Arria V GZ devices, the Interlaken module is an instance of the Interlaken PHY IP core

configured for duplex operation, and is generated by the Quartus II parameter editor. The core requires a

Stratix V Transceiver Reconfiguration Controller for transceiver calibration. The duplex core initially

requires as many reconfiguration interfaces as the number of lanes that the IP core usesplus one for the

TX PLL.

Related Information

•

For more information about the Arria 10 Native PHY IP core.

•

For more information about the Interlaken PHY IP core.

Arria 10 versus Stratix V and Arria V GZ Variations

The Arria 10 transceiver is different than the Stratix V or Arria V GZ transceiver. Therefore, the

SerialLite III IP core is implemented differently for these device families, and the example testbenches are

also different.

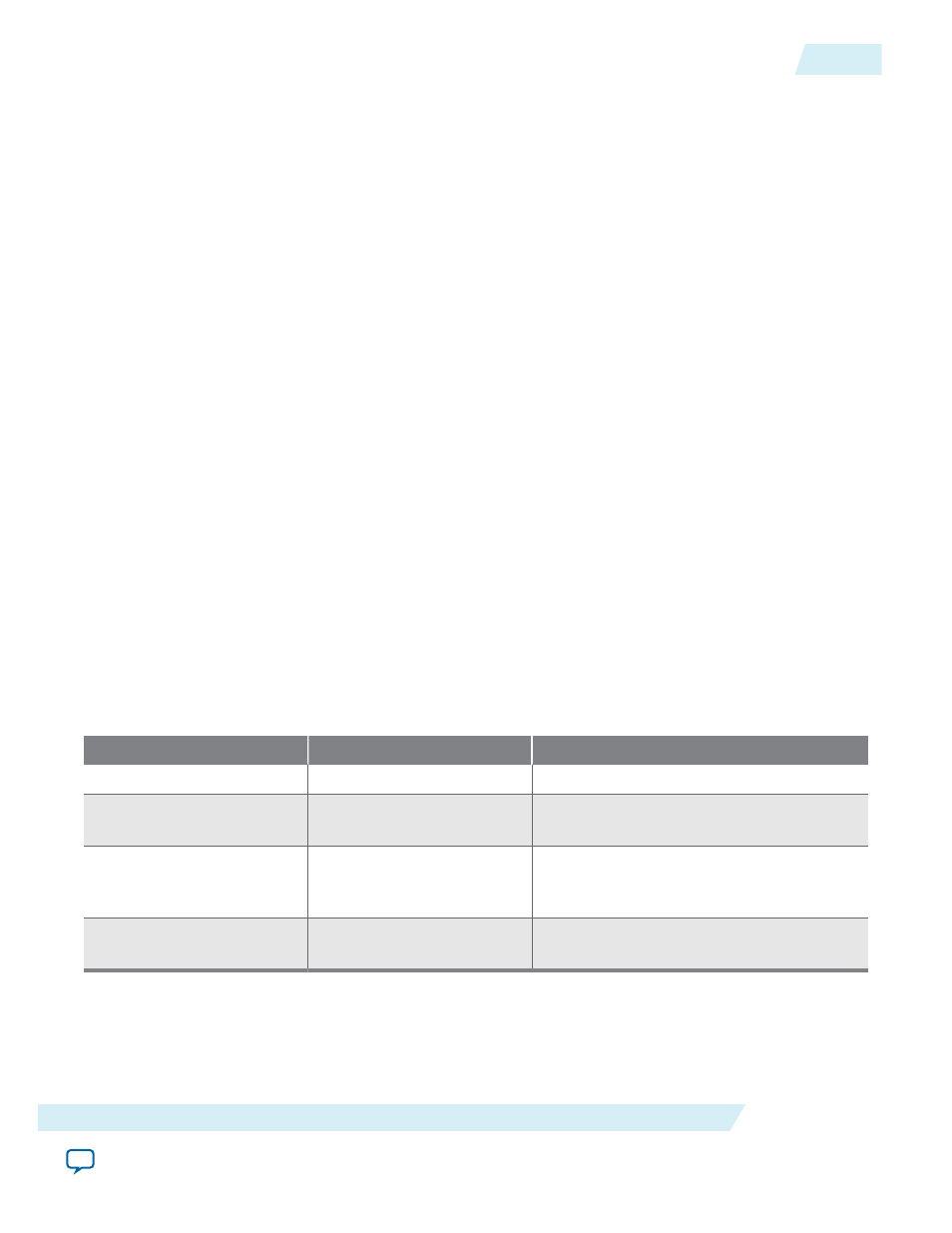

Table 4-2: Differences between Arria 10 and Stratix V or Arria V GZ Transceivers

Implementation

Arria 10

Stratix V or Arria V GZ

Transceiver PLL

Not included

Included

Transceiver Reconfigura‐

tion Controller

Not required

Required

Example Testbench

Generated dynamically (same

configuration as the IP core

instance)

Generated dynamically (same configuration

as the IP core instance)

Hardware Demonstration

Design Example

Not included

Included

When you create an instance of the IP core, it generates an example testbench dynamically. This testbench

has the same configuration as the IP core instance.

For Arria 10 devices, the Native PHY IP core (Interlaken mode) requires an external transmit PLL.

Instantiate the external transceiver PLLs and then connect the transmit serial clock output to the

UG-01126

2015.05.04

SerialLite III Streaming Duplex Core

4-9

SerialLite III Streaming IP Core Functional Description

Altera Corporation