Standard clocking mode – Altera SerialLite III Streaming MegaCore Function User Manual

Page 36

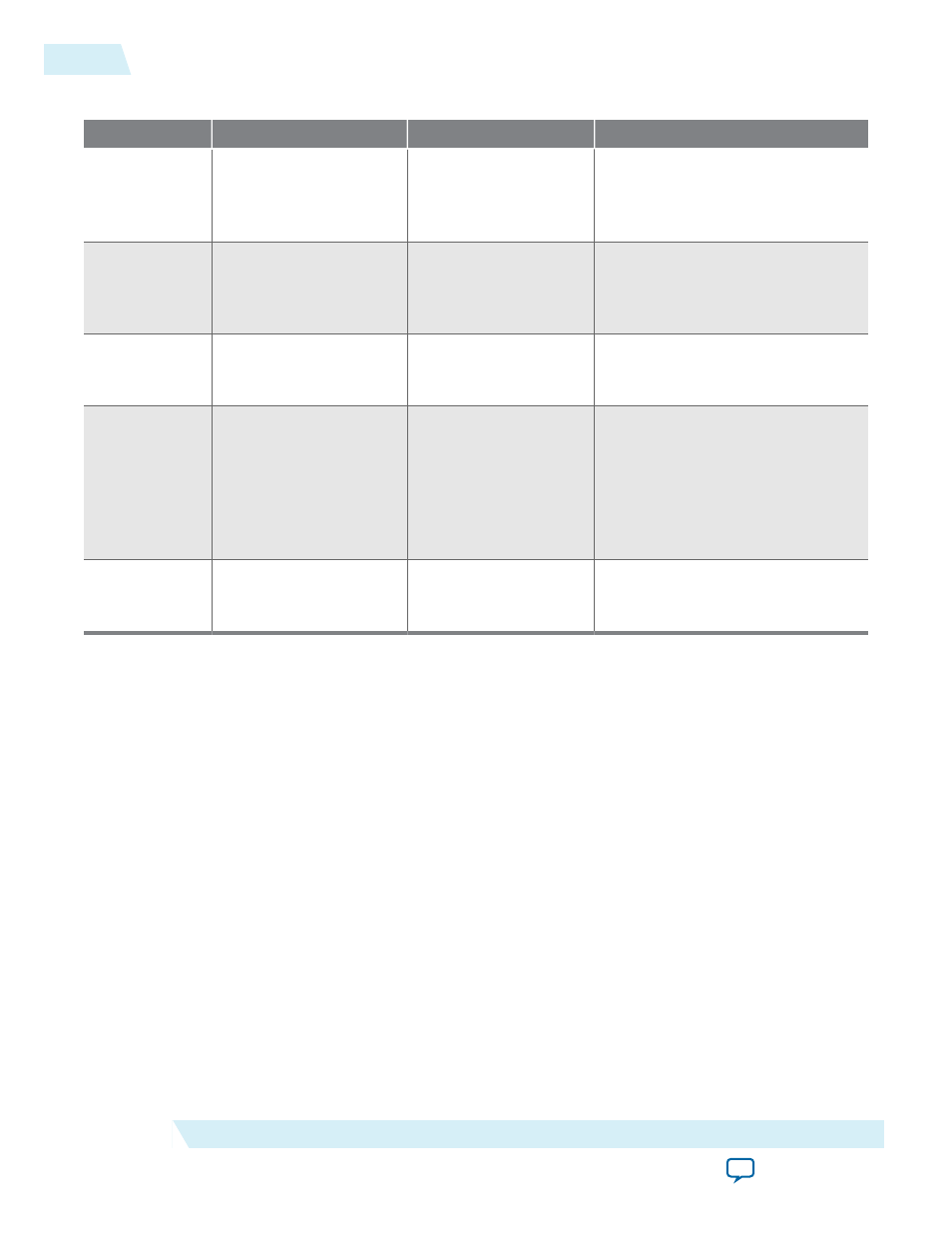

Table 4-4: Comparing Standard and Advanced Clocking Modes

Resource

Standard Mode

Advanced Mode

Description

Source user

clocking

Core generated

User provided

If the PPM difference between the

generated and user clocks is not

acceptable, use the advanced

clocking mode.

MAC fPLL

Uses one fPLL per

direction

Does not use fPLLs

If the design uses many fPLLs and

clock crossing is an issue in the

user environment, use the

advanced clocking mode.

Transmission

overhead

1.1 x <input data rate>

<Interlaken Overhead> x

<input data rate>

The advanced clocking mode

overhead is less than the standard

clocking mode overhead.

Streaming

variation

Pure streaming where the

output data appears

exactly as it was input

Output streaming data is

accompanied by

numerous empty clock

cycles

If empty cycles (where no valid

data is present) at the output are

intolerable, use pure streaming

(standard clocking mode).

Alternatively, create your own sink

interface to remove the empty

cycles.

Sink interface Fixed

You can include your

own logic or FIFO to

receive the output data

on

page 4-13

Standard Clocking Mode

In the standard clocking mode, the SerialLite III Streaming IP core operates in a pure streaming manner,

exactly replicating the source input data at the sink end. The SerialLite III Streaming IP core generates the

user clock at both the source and sink to drive the user interface.

In this mode, you initially specify the user clock frequency through the SerialLite III Streaming parameter

editor. The Quartus II software then automatically calculates the reference clock coming from the Native

PHY or Interlaken PHY IP core and the two clock outputs from the fPLL in the clock generator module.

After the calculation, the Quartus II software provides a list of transceiver reference clock values for you to

select. Depending on the clock constraints, the generated value for the user clock should be very close, if

not identical, to the user clock frequency that you specify. The Quartus II software shows the generated

user clock value as well as transceiver reference clock values.

4-12

Standard Clocking Mode

UG-01126

2015.05.04

Altera Corporation

SerialLite III Streaming IP Core Functional Description