Arria 10 simulation testbench, Arria 10 simulation testbench -12, Arria 10 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 21: Simulation testbench

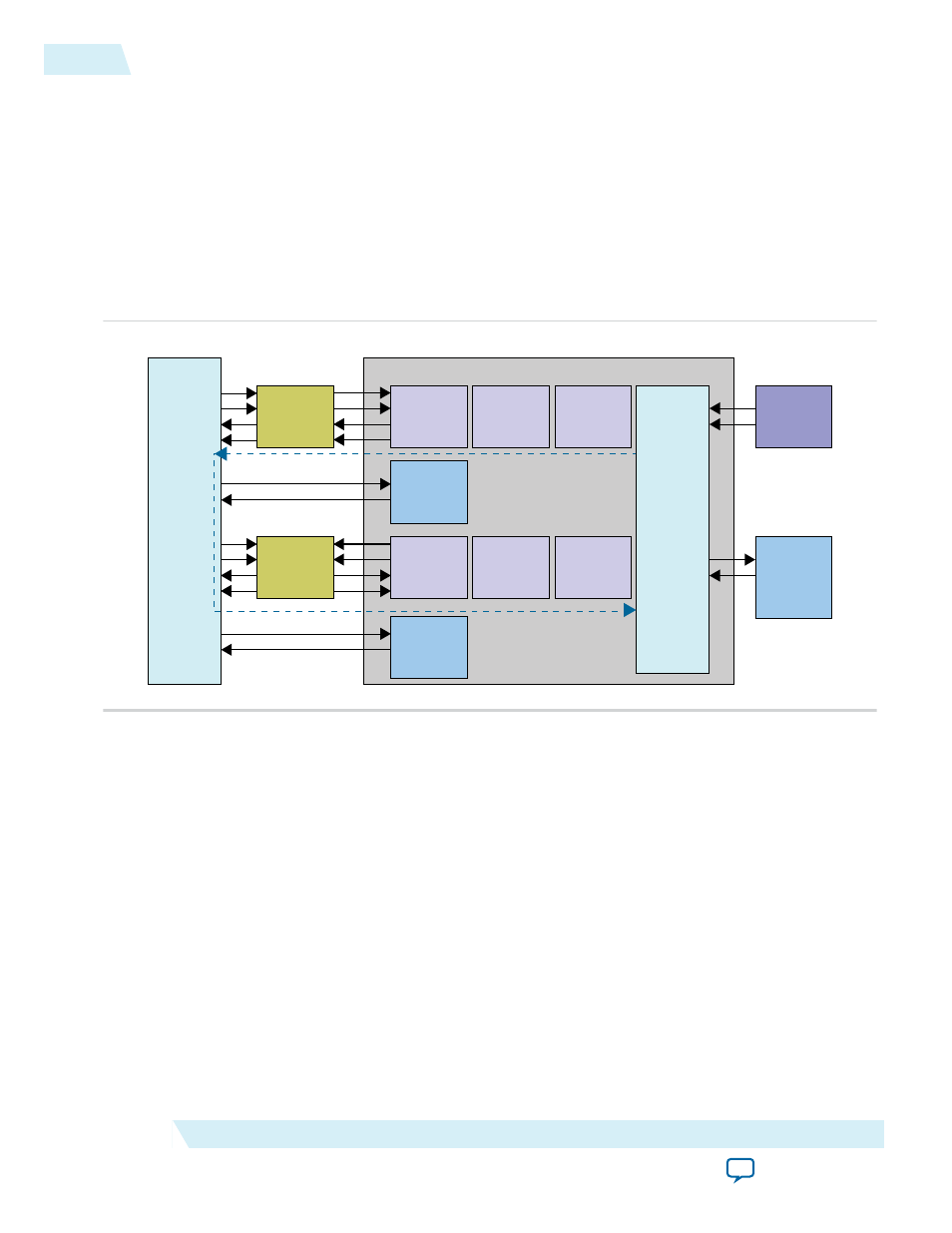

Arria 10 Simulation Testbench

If your design targets Arria 10 devices, the generated example testbench is dynamic and has the same

configuration as the IP (except for the metaframe length). When you choose the sink or duplex direction,

the parameter editor generates an external transceiver ATX PLL for use in the Arria 10 testbench.

Therefore, Altera recommends that you generate the Arria 10 simulation testbench for designs using the

sink or duplex direction.

Note: The Arria 10 example testbench includes the external transceiver PLL; the IP core does not include

the transceiver PLL for these devices.

Figure 3-5: SerialLite III Streaming Example Testbench (Duplex) for Arria 10 Devices

Testbench

Traffic

Generator

Traffic

Checker

Source

Absorber

Source

Application

Source

Adaptation

Sink

Application

Sink

Adaptation

Sink

Alignment

Source

Clock

Generator

Sink

Clock

Generator

Native

PHY IP

Duplex -

Interlaken

Mode

Transceiver

TX PLL

Skew

Insertion

Loopback

Device Under Test (Duplex Mode)

Test Environment

3-12

Arria 10 Simulation Testbench

UG-01126

2015.05.04

Altera Corporation

Getting Started