Altera SerialLite III Streaming MegaCore Function User Manual

Page 49

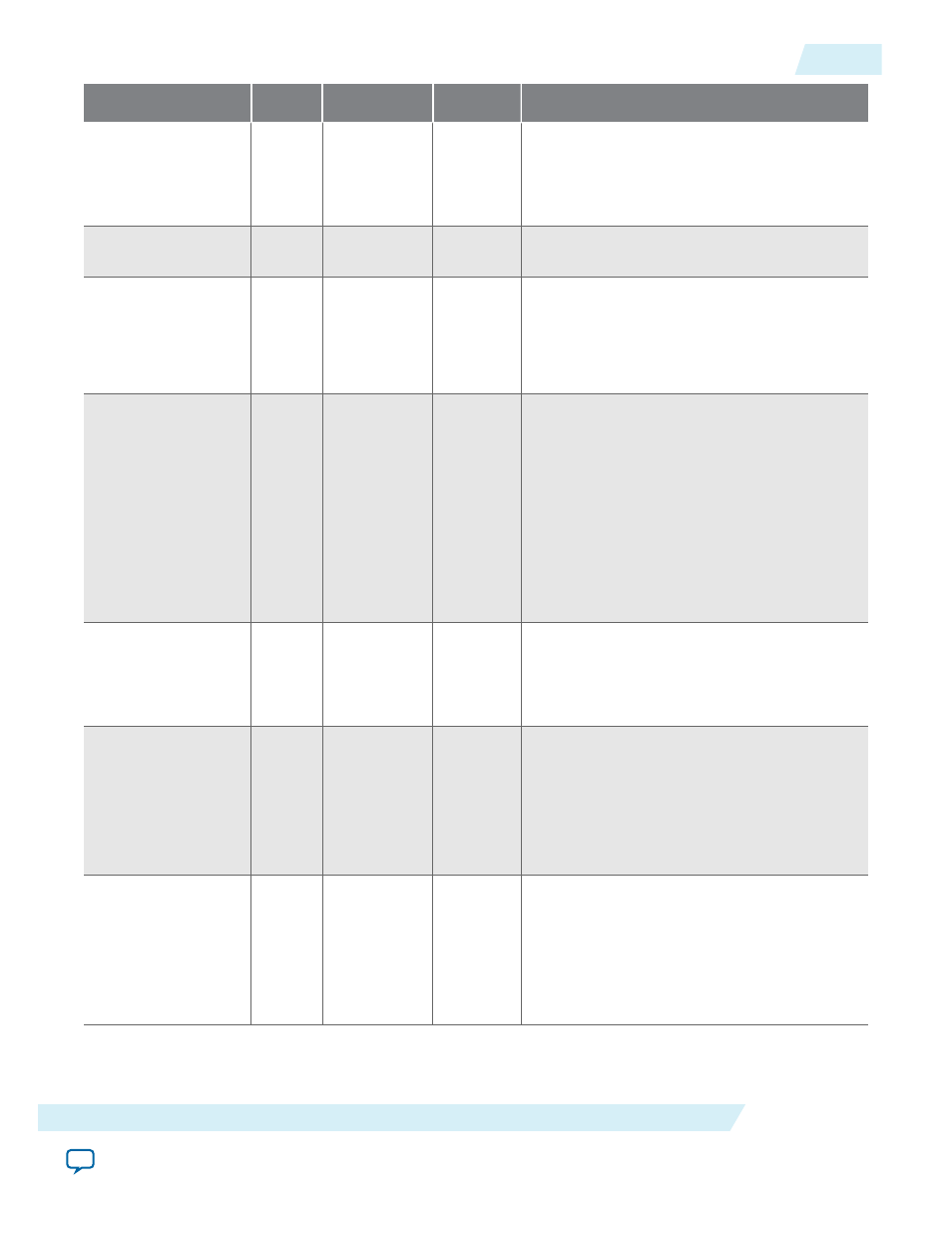

Signal

Width

Clock Domain

Direction

Description

core_reset

1

N.A.

Input

Asynchronous master reset for the core.

Assert this signal high to reset the MAC

layer, except for the fPLL that is available in

Standard Clocking Mode.

xcvr_pll_ref_

clk

1

N.A.

Input

Reference clock for the transceivers.

user_clock_tx

1

N.A.

Input/

Output

Clock for data transfers across the transmit

interface.

• Input: Using advanced clocking mode

• Output: Using standard clocking mode

user_clock_

reset_tx

1

user_clock_tx Input/

Output

In the standard clocking mode, the core

asserts this signal when the

core_reset

signal is high and deasserts this signal when

the reset sequence is complete.

In the advanced clocking mode, the core

asserts this signal to reset the adaptation

module FIFO buffer.

• Input: Using advanced clocking mode

• Output: Using standard clocking mode

interface_

clock_reset_tx

1

core_clock

Output

In the advanced clocking mode, the core

asserts this signal when the

core_reset

signal is high and deasserts this signal when

the reset sequence is complete.

link_up_tx

1

Standard

clocking:

user_clock

Advanced

clocking:

core_clock

Output

The core asserts this signal to indicate that

the core initialization is complete and is

ready to transmit user data.

data_tx

64xN

Standard

clocking:

user_clock

Advanced

clocking:

core_clock

Input

This vector carries the transmitted streaming

data to the core.

N represents the number of lanes.

UG-01126

2015.05.04

Signals

4-25

SerialLite III Streaming IP Core Functional Description

Altera Corporation