Crc-32 error injection, Fifo ecc protection, User data interface waveforms – Altera SerialLite III Streaming MegaCore Function User Manual

Page 41: Crc-32 error injection -17, Fifo ecc protection -17, User data interface waveforms -17

CRC-32 Error Injection

In the Quartus II software version 13.1 and higher, the SerialLite III IP core supports CRC error injection

with the 10G PCS CRC-32 generator. This feature enables corruption of the CRC-32 value of the CRC-32

generator.

To insert CRC errors for a given lane, the IP interface includes a CRC error injection control signal.

Asserting this control signal inserts CRC errors for all the lanes and transceivers that have enabled

support for error injection. You can enable the CRC error injection for a specific transceiver channel

(SerialLite III lane) by programming the appropriate transceiver PCS CRAM bit. The provided example

design demonstrates how set the respective CRAM bits using the NIos II processor.

Related Information

SerialLite III Streaming IP Core Design Example for Stratix V Devices

FIFO ECC Protection

In the Quartus II software version 13.1 and higher, the SerialLite III IP core can be protected from Single-

Event Upset (SEU) changes using error correcting code (ECC) protection. You enable this feature using

the ECC protection option in the parameter editor. The ECC protection provides additional error status

bits that tell you if the ECC was able to perform a correction from the SEU change or if an uncorrectable

error has occurred.

Note: Enabling ECC protection incurs additional logic and latency overhead.

User Data Interface Waveforms

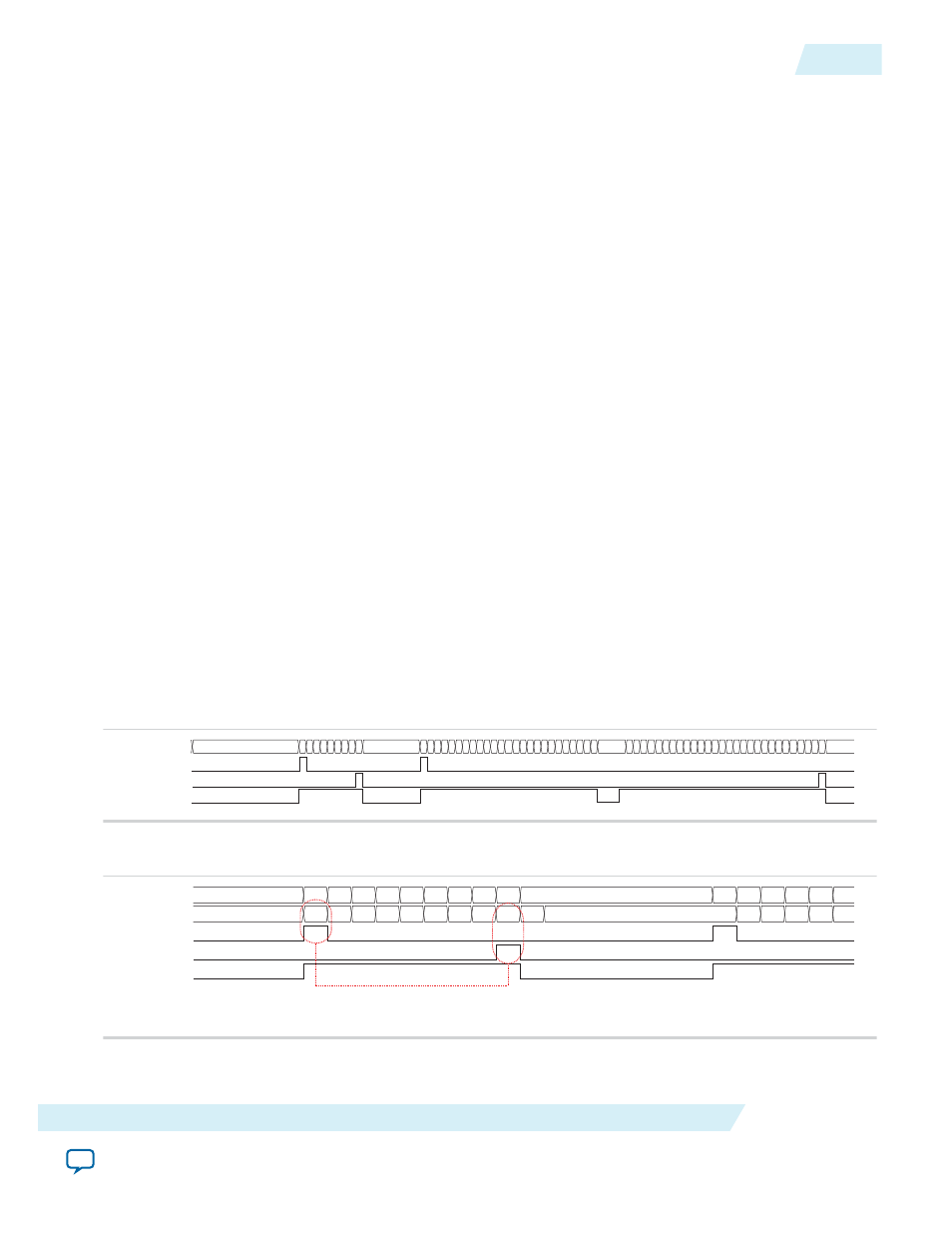

The following waveforms apply to the source user interface in source-only and duplex cores.

Figure 4-10: Source Waveform for Burst Mode

1800_0020_0000_0*

1800_002*

180*

180*

*

*

*

data[127:0]

start_of_burst

end_of_burst

valid

Figure 4-11: Source Waveform for Burst Mode (Sync)

1800_0020_0000_06*

data[127:0]

sync[7:0]

start_of_burst

end_of_burst

valid

18* 18* 18* 18* 18* 18* 18* 18* 18* 1800_0021_0000_06e1_2000_0021_0*

18* 18* 18* 18* 18* 18*

0

4

0

0

0

9

3

c

a

3

8

a

a

8

f

e

The source sync data are picked

up at the start_of_burst and end_of_burst cycle.

5

UG-01126

2015.05.04

CRC-32 Error Injection

4-17

SerialLite III Streaming IP Core Functional Description

Altera Corporation