Altera SerialLite III Streaming MegaCore Function User Manual

Page 44

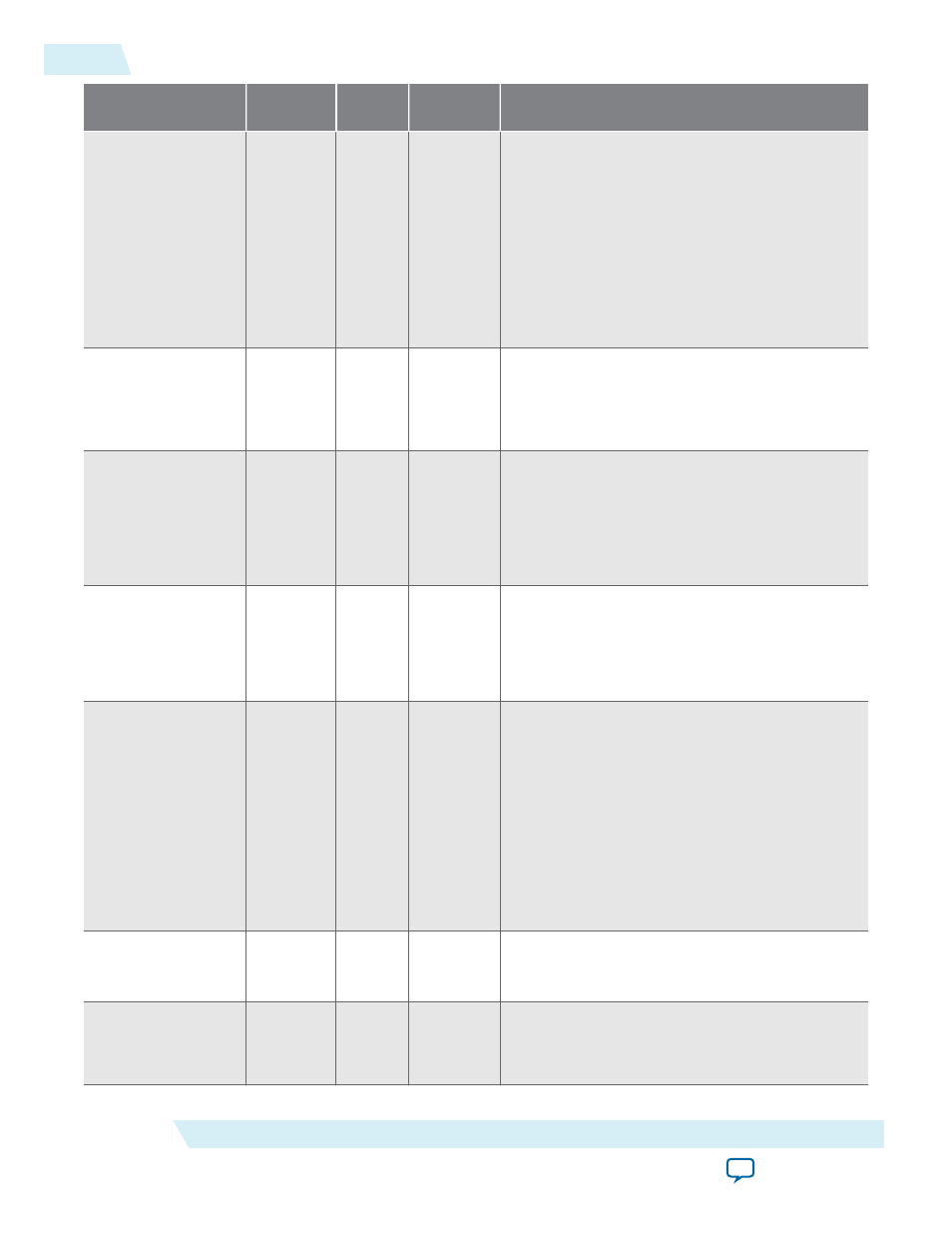

Signal

Width

Clock

Domain

Direction

Description

tx_pll_locked

1

N.A.

Input

This signal indicates that all external transceiver

PLLs are locked. If more than one external

transceiver PLL is required for higher lanes, each

instantiation outputs a bit that indicates whether

the PLL providing the high-speed clock for a

corresponding transceiver has achieved its lock

status. The

pll_locked

output signal from the

external transceiver PLLs should be ANDed

together before being input to the IP core. (Arria

10 devices only)

core_reset

1

N.A.

Input

Asynchronous master reset for the core. Assert

this signal high to reset the MAC layer, except

for the fPLL that is available in standard

clocking mode.

xcvr_pll_ref_

clk

1

N.A.

Input

For Stratix V and Arria V GZ devices, this

signals is the reference clock for the transceivers.

For Arria 10 devices, this signal is present but

unused in source-only variations; tie this signal

to 1’b0.

user_clock

1

N.A.

Input/

Output

Clock for data transfers across the source core

interface.

• Input: Using advanced clocking mode

• Output: Using standard clocking mode

user_clock_

reset

1

user_

clock

Input/

Output

In the standard clocking mode, the core asserts

this signal when the

core_reset

signal is high

and deasserts this signal when the reset sequence

is complete.

In the advanced clocking mode, the core asserts

this signal to reset the adaptation module FIFO

buffer.

• Input: Using advanced clocking mode

• Output: Using standard clocking mode

reconfig_clk

1

N.A.

User

application

to IP core

This clock is for the transceiver reconfiguration

interface. It also sequences the reset state

machine in the clock generation logic.

link_up

1

user_

clock

Output

The core asserts this signal to indicate that the

core initialization is complete and is ready to

transmit user data.

4-20

Signals

UG-01126

2015.05.04

Altera Corporation

SerialLite III Streaming IP Core Functional Description