Altera SerialLite III Streaming MegaCore Function User Manual

Page 45

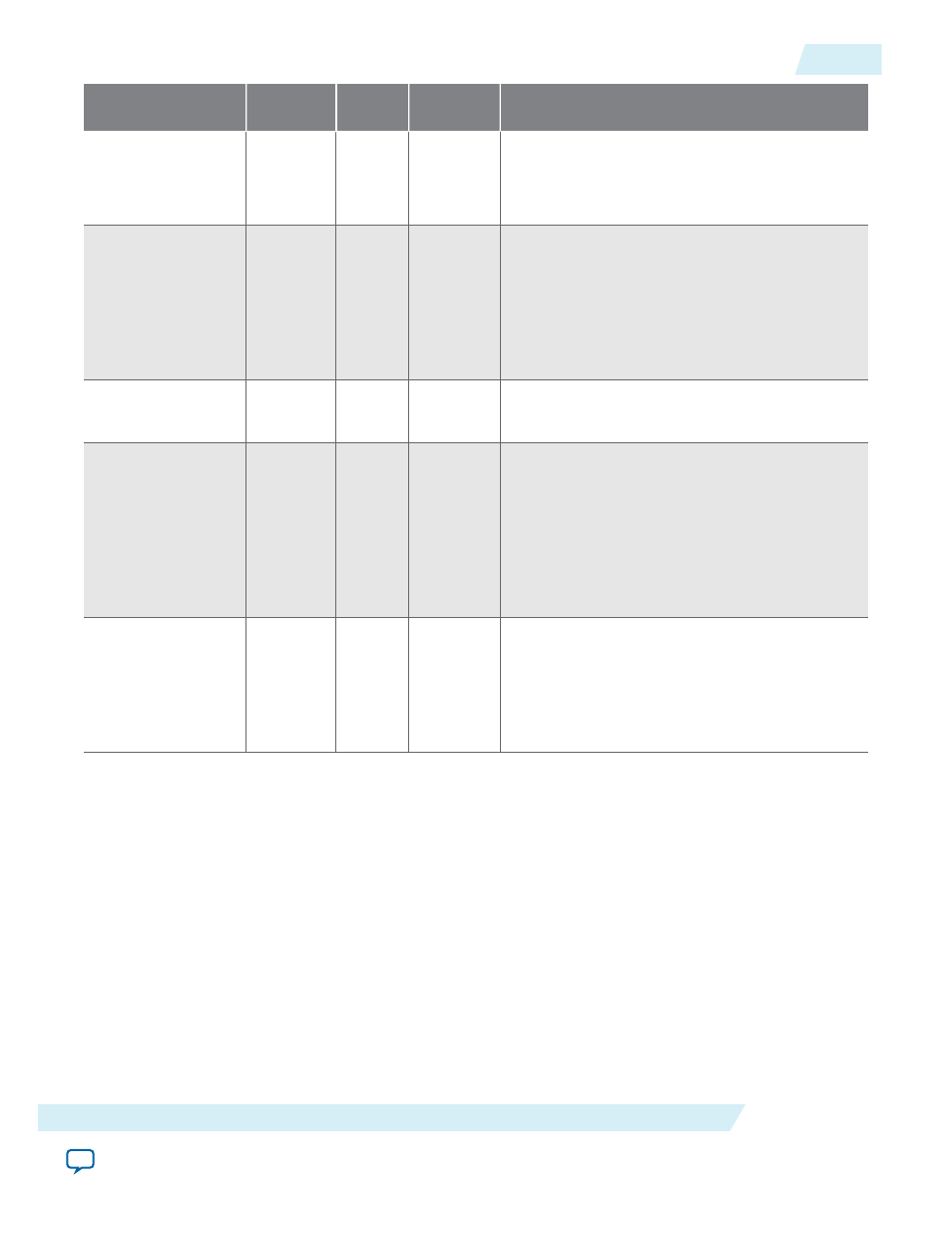

Signal

Width

Clock

Domain

Direction

Description

data

64xN

user_

clock

Input

This vector carries the transmitted streaming

data to the core.

N represents the number of lanes.

sync

8

user_

clock

Input

The sync vector is an 8 bit bus. The data value at

the start of a burst and the end of a burst are

captured and transported across the link.

Note: This vector is not associated with

Interlaken channelization or flow

control schemes.

valid

1

user_

clock

Input

This single bit signal indicates that the

transmitted streaming data is valid.

start_of_burst

1

user_

clock

Input

When the core is in burst mode operation,

asserting this signal indicates that the informa‐

tion on the data vector is the beginning of a

burst.

Because continuous mode is one long burst, in

this mode the signal is asserted only once at the

start of the data.

end_of_burst

1

user_

clock

Input

When the core is in burst mode operation,

asserting this signal indicates that the informa‐

tion on the data vector is the end of a burst.

You can optionally send an end of burst signal at

the end of continuous mode.

UG-01126

2015.05.04

Signals

4-21

SerialLite III Streaming IP Core Functional Description

Altera Corporation