Altera SerialLite III Streaming MegaCore Function User Manual

Page 51

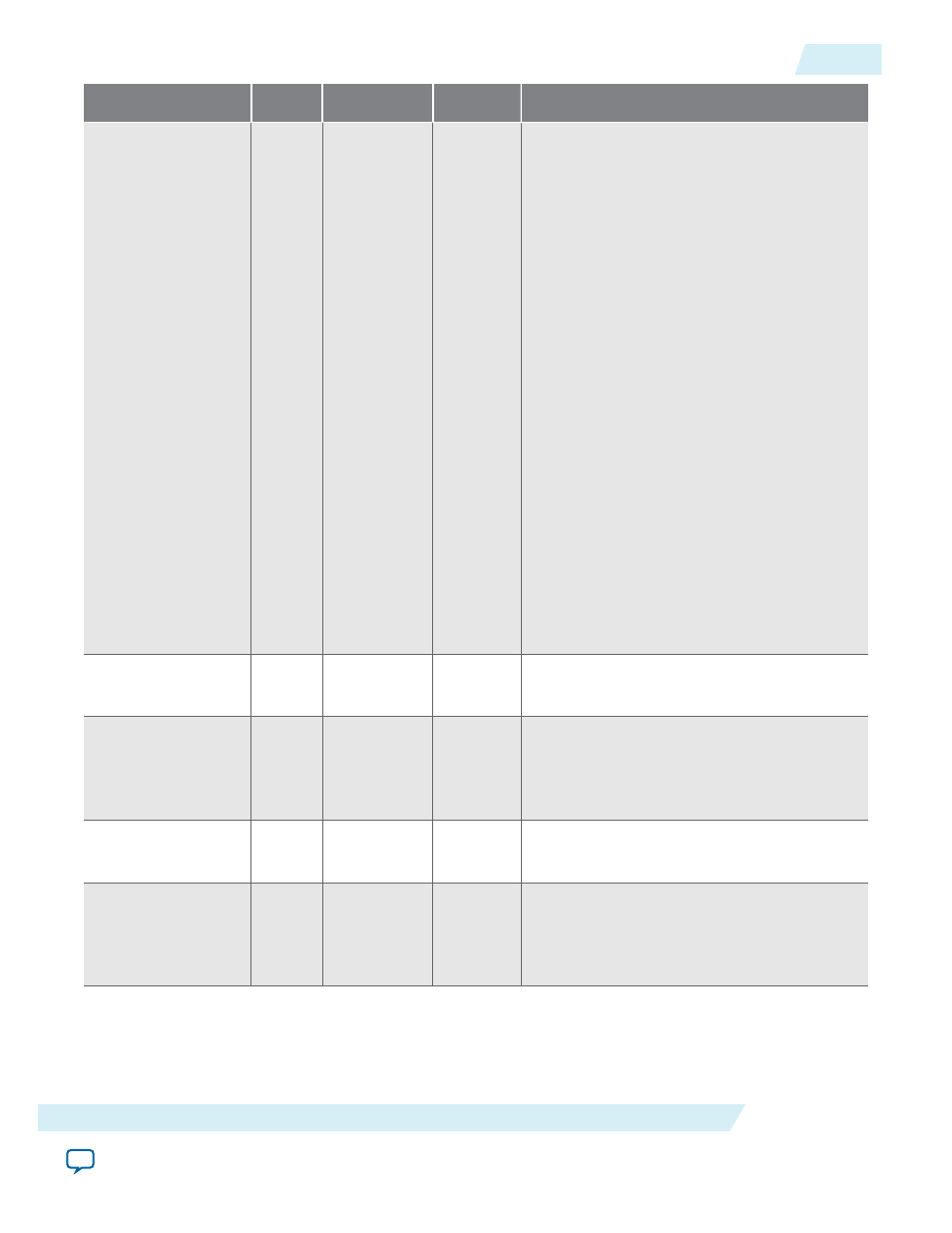

Signal

Width

Clock Domain

Direction

Description

error_tx

3 or 4

Standard

clocking:

user_clock

Advanced

clocking:

core_clock

Output

This vector indicates an overflow in the

source adaptation module’s FIFO buffer.

• Bit 0: Source adaptation module’s FIFO

buffer overflow

• Bit 1: Source PPM-absorption module’s

FIFO buffer overflow

ECC option:

• MSB-1: An SEU error occurred and was

corrected (ECC enabled). This bit is bit 2

in advanced clocking mode and bit 1 in

standard clocking mode.

Don't care (ECC disabled)

• MSB: An SEU error occurred and could

not be corrected (ECC enabled). This bit

is bit 3 in advanced clocking mode and bit

2 in standard clocking mode.

Don't care (ECC disabled)

The width of this signal depends on the

clocking mode:

• 3: Using standard clocking mode

• 4: Using advanced clocking mode

user_clock_rx

1

N.A.

Output

Clock for data transfers across the sink core

interface in the standard clocking mode.

user_clock_

reset_rx

1

user_clock_rx Output

In the standard clocking mode, the core

asserts this signal when the

core_reset

signal is high and deasserts this signal when

the reset sequence is complete.

interface_

clock_rx

1

core_clock

Output

Clock for data transfers across the sink core

interface in the advanced clocking mode.

interface_

clock_reset_rx

1

core_clock

Output

In the advanced clocking mode, the core

asserts this signal when the

core_reset

signal is high and deasserts this signal when

the reset sequence is complete.

UG-01126

2015.05.04

Signals

4-27

SerialLite III Streaming IP Core Functional Description

Altera Corporation