Simulation parameters, Simulation parameters -10 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 19

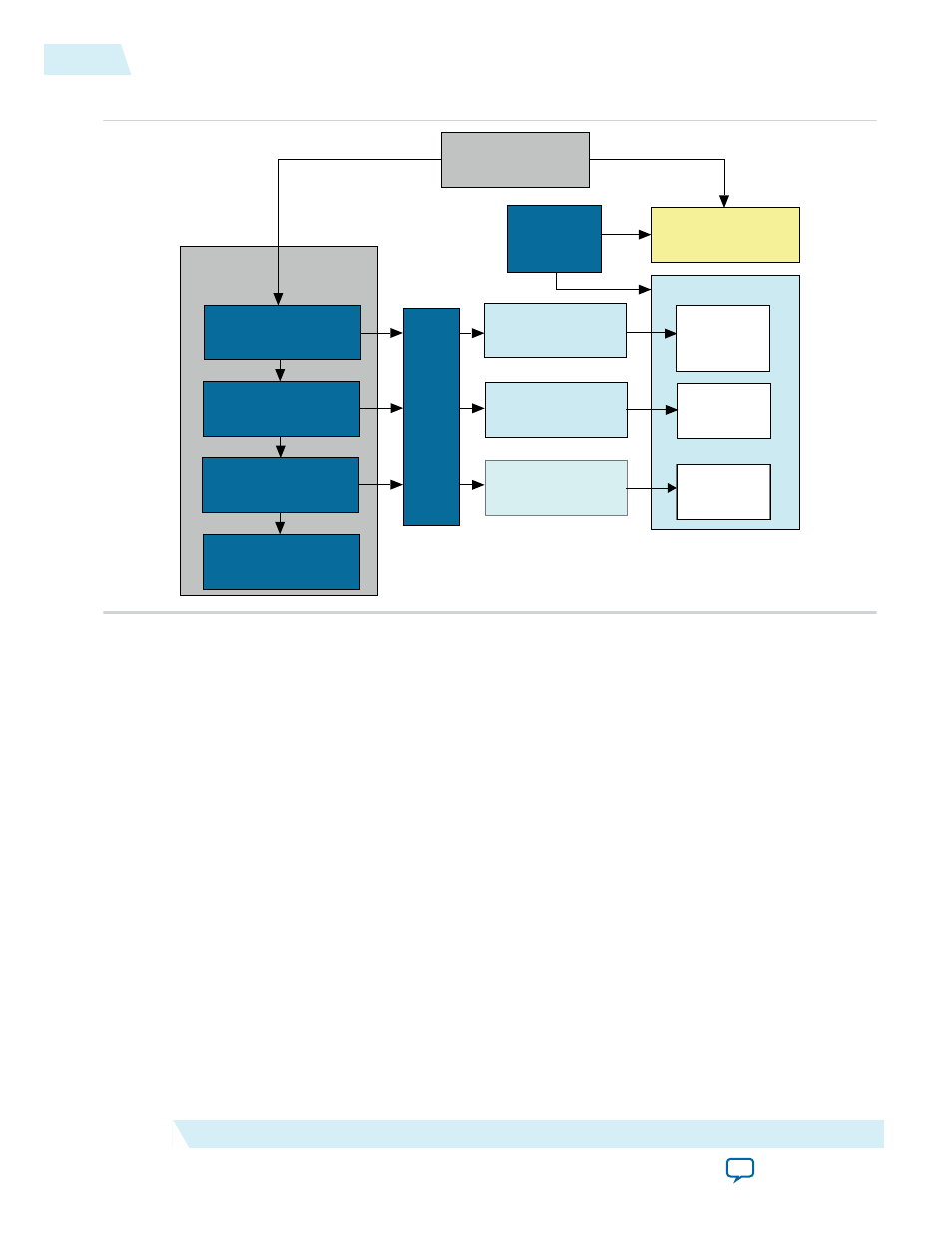

Figure 3-4: Simulation in Quartus II Design Flow

Post-fit timing

simulation netlist

Post-fit timing

simulation

(3)

Post-fit functional

simulation netlist

Post-fit functional

simulation

Analysis & Synthesis

Fitter

(place-and-route)

TimeQuest Timing Analyzer

Device Programmer

Quartus II

Design Flow

Gate-Level Simulation

Post-synthesis

functional

simulation

Post-synthesis functional

simulation netlist

(Optional) Post-fit

timing simulation

RTL Simulation

Design Entry

(HDL, Qsys, DSP Builder)

Altera Simulation

Models

EDA

Netlist

Writer

Note: Post-fit timing simulation is supported only for Stratix IV and Cyclone IV devices in the current

version of the Quartus II software. Altera IP supports a variety of simulation models, including

simulation-specific IP functional simulation models and encrypted RTL models, and plain text

RTL models. These are all cycle-accurate models. The models support fast functional simulation of

your IP core instance using industry-standard VHDL or Verilog HDL simulators. For some cores,

only the plain text RTL model is generated, and you can simulate that model. Use the simulation

models only for simulation and not for synthesis or any other purposes. Using these models for

synthesis creates a nonfunctional design.

Related Information

Simulation Parameters

After design generation, simulation files are available for you to simulate your design. To simulate your

design, ensure that the SerialLite III Streaming IP core source and sink cores are both generated with the

same parameters or are duplex cores.

• Stratix V and Arria V GZ files are located in the <variation name>_sim directory

• Arria 10 files are located in the <variation name> directory

The example testbench simulates the core using the user-specified configuration

3-10

Simulation Parameters

UG-01126

2015.05.04

Altera Corporation

Getting Started