Error handling, Error handling -10 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 65

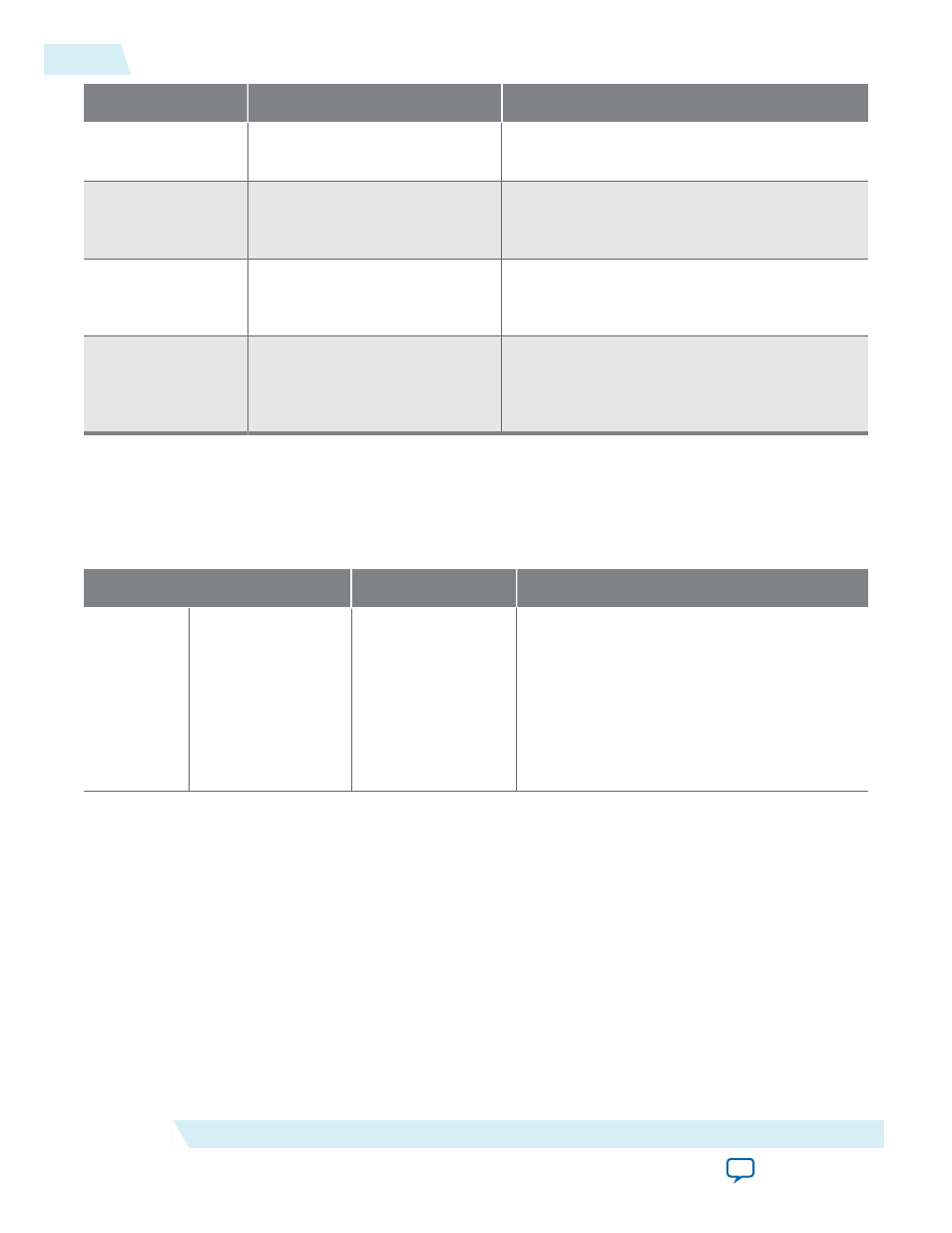

Signal Name

Location

Description

rx_crc32

/sink/rx_crc32

This active high signal indicates CRC-32 error

from the CRC checker.

rx_frame_lock

[lanes-1:0]

/sink/rx_frame_lock

This active high signal indicates that four

Interlaken synchronization words are found for

a given lane.

rx_is_lockedto-

data [lanes-

1:0]

/sink/Interlaken_phy_ip_rx/sv_

ilk_inst

This active high signal indicates that the

transceiver channel PLL has locked itself to the

incoming data.

rx_cal_busy

/sink/Interlaken_phy_ip_rx/sv_

ilk_inst

Sink transceiver calibration status. This active

high signal can be used for debugging if the

reconfiguration controller is actively calibrating

during the initialization sequence.

Error Handling

Table 5-4: Error Conditions and Core Behavior

This table lists the error conditions that the core detect and their behavior in response to each condition.

Condition

Error Indication

Core Behavior

Source

Core

Rate adaptation FIFO

buffer overflow in

source interface

The source core

asserts the error flag

for one clock cycle.

There is an overflow on the rate adaptation

FIFO buffer in the source interface. The core

behavior depends on the operation mode:

• Continuous mode—error is flagged once

an overflow is detected.

• Burst mode—error is flagged only when an

overflow occurs during burst data transfer

across the user interface.

5-10

Error Handling

UG-01126

2015.05.04

Altera Corporation

SerialLite III Streaming IP Core Design Guidelines