Arria 10 designs, Seriallite iii streaming ip core parameters, Arria 10 designs -3 – Altera SerialLite III Streaming MegaCore Function User Manual

Page 12: Seriallite iii streaming ip core parameters -3

Arria 10 Designs

If your design targets Arria 10 devices:

• The parameter editor displays a message about the required output clock frequency of the external TX

PLL IP clock. For source or duplex modes, connect the Transceiver PHY Reset Controller to the TX

PLL to ensure the appropriate HSSI power-up sequence.

• For source only Arria 10 implementations, the parameter editor does not provide the transceiver

reference clock frequency because the user is expected to provide the transmit serial clock. If you use

an on-chip PLL to generate the transmit serial clock, you can use the same PLL reference clock

frequency that you provide to the core in the sink direction, operating at the same user clock frequency

(or equivalent transceiver lane data rate).

• The SerialLite IP core expects the user to provide the transmitter's serial clock. If you compile the IP

without the proper serial clock, the Quartus II Compiler issues a compilation error. Refer to

for an example design.

• When generating the example testbench, the SerialLite IP core instantiates an external transceiver ATX

PLL for the transmit serial clock based on the required user clock only when configured in sink or

duplex mode. The Arria 10 simulation testbench uses the external transceiver ATX PLL. The

transceiver ATX PLL core is configured with the transceiver reference clock specified in the parameter

editor and transmit serial clock.

• To generate the SerialLite III Arria 10 example testbench using the parameter editor, select Generate >

Example Designs > seriallite_iii_a10_0 - example (alternatively, turn on the Example Design option

in the parameter editor). Altera recommends that you generate the Arria 10 simulation testbench for

the sink or duplex direction.

Related Information

•

SerialLite III Streaming IP Core Parameters

on page 3-3

•

•

Arria 10 versus Stratix V and Arria V GZ Variations

on page 4-9

SerialLite III Streaming IP Core Parameters

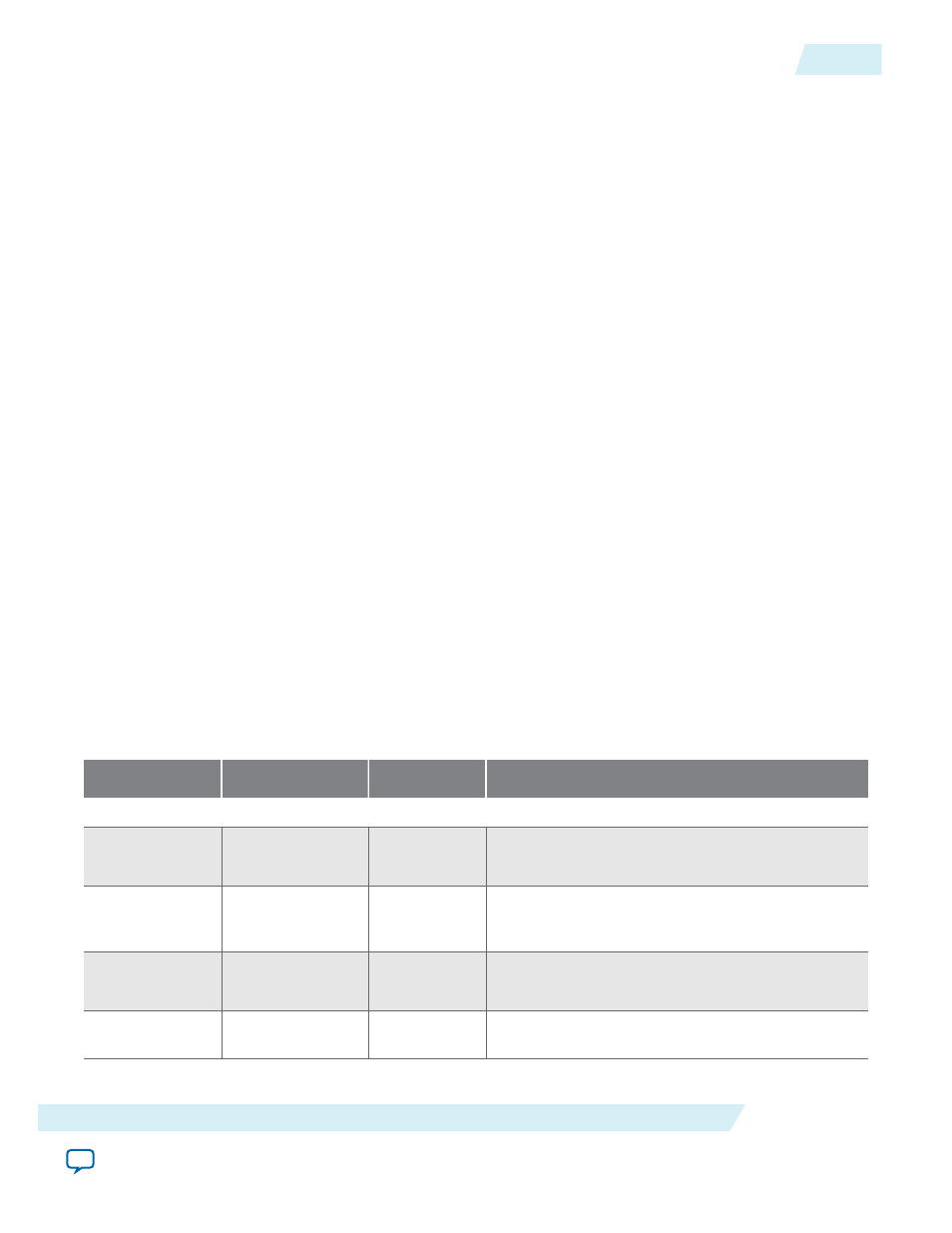

Table 3-1: SerialLite III Streaming IP Core Parameters

Parameter

Value

Default

Description

General Design Options

Direction

Source, Sink,

Duplex

Duplex

Indicates the direction of the core's variant.

Lanes

1–24

4

Specifies the number of lanes (equal to physical

transceiver links) that are used to transfer the

streaming data.

Device speed

grade

1–4

2

Specifies the device speed grade (Stratix V and

Arria V GZ devices only).

PLL type

ATX, CMU

CMU

Selects the transceiver PLL type. (Stratix V and

Arria V GZ devices only)

UG-01126

2015.05.04

Arria 10 Designs

3-3

Getting Started

Altera Corporation