Altera SerialLite III Streaming MegaCore Function User Manual

Page 20

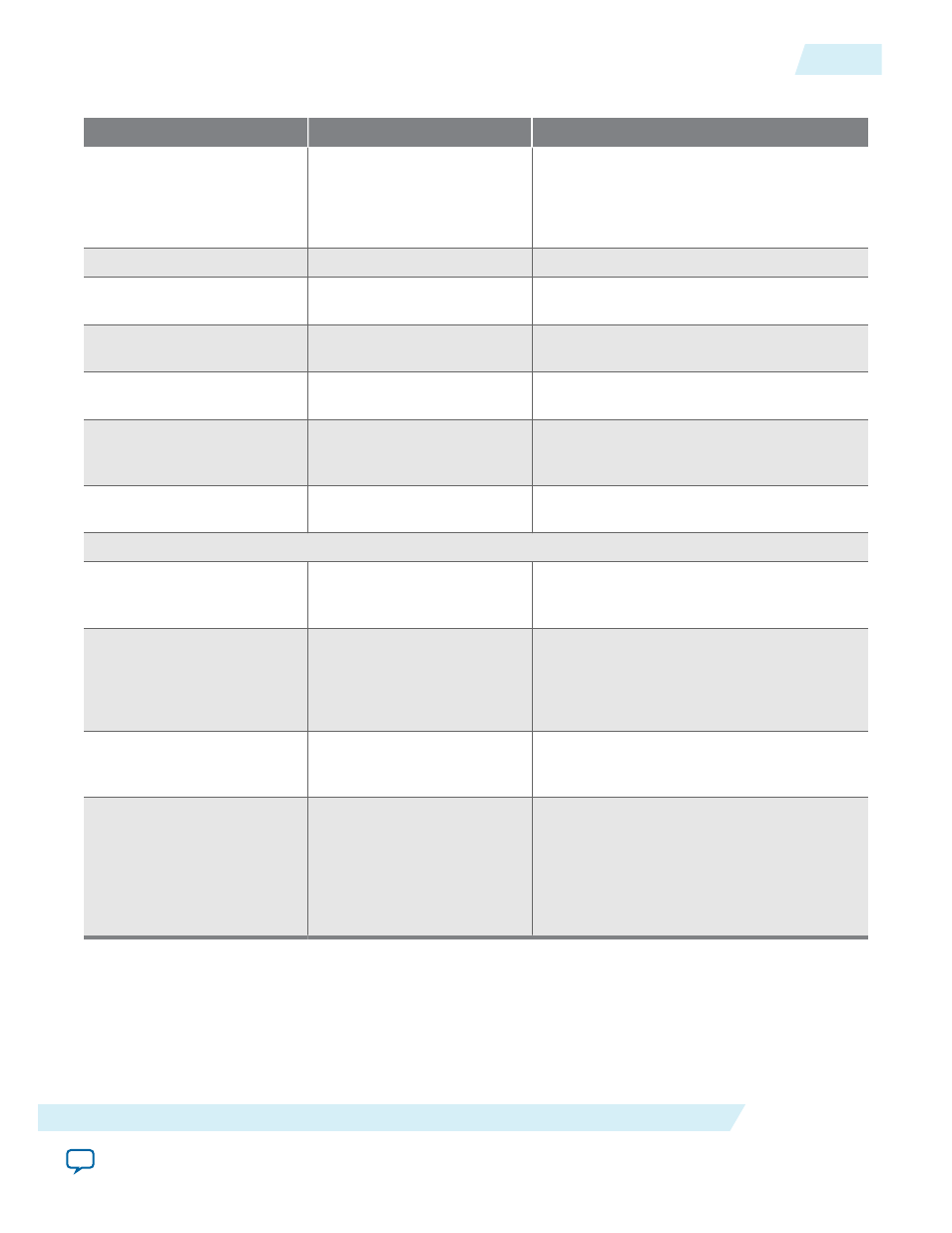

Table 3-3: Stratix V and Arria V GZ Testbench Default Simulation Parameters

Parameter

Default Value

Comments

Generated user clock

frequency (

user_clock_

frequency

)

Standard clocking: 145.98375

MHz

Advanced clocking:

146.484375

—

Lanes (

lanes

)

2

—

Transceiver reference clock

frequency (

pll_ref_freq

)

644.53125 MHz

—

Transceiver data rate per

lane (

data_rate

)

10312.5 Mbps

—

Meta frame length (

meta_

frame_length

)

200

—

fPLL reference clock

frequency (

reference_

clock_frequency

)

257.8125 MHz

Not used in advanced clocking mode.

Core clock frequency

(

coreclkin_frequency

)

205.078125 MHz

Not used in advanced clocking mode.

Simulation-specific parameters

Total samples to transfer

(

total_samples_to_

transfer

)

2000

Total samples to transfer during simulation.

Mode (

mode

)

Continuous/burst

The testbench environment may automati‐

cally choose one of the modes depending on

the random seed with which it is provided.

Refer to the simulation scripts listed in

for details.

Skew insertion enable

(

skew_insertion_enable

)

Yes

Skew testing is enabled. The testbench

environment randomly inserts skew in the

lanes within the range 0 - 107 UI.

ECC protection enabled

(

ecc_enable

)

0

When set, the core is simulated with the

ECC-enabled variant. Use the ECC-enabled

variant in the test environment.

When ECC mode is disabled, the two most

significant bits of the error buses in the

source or sink direction are don't care.

For more information about Altera simulation models, refer to the Simulating Altera Designs chapter in

volume 3 of the Quartus II Handbook.

Related Information

UG-01126

2015.05.04

Simulation Parameters

3-11

Getting Started

Altera Corporation