Altera SerialLite III Streaming MegaCore Function User Manual

Page 53

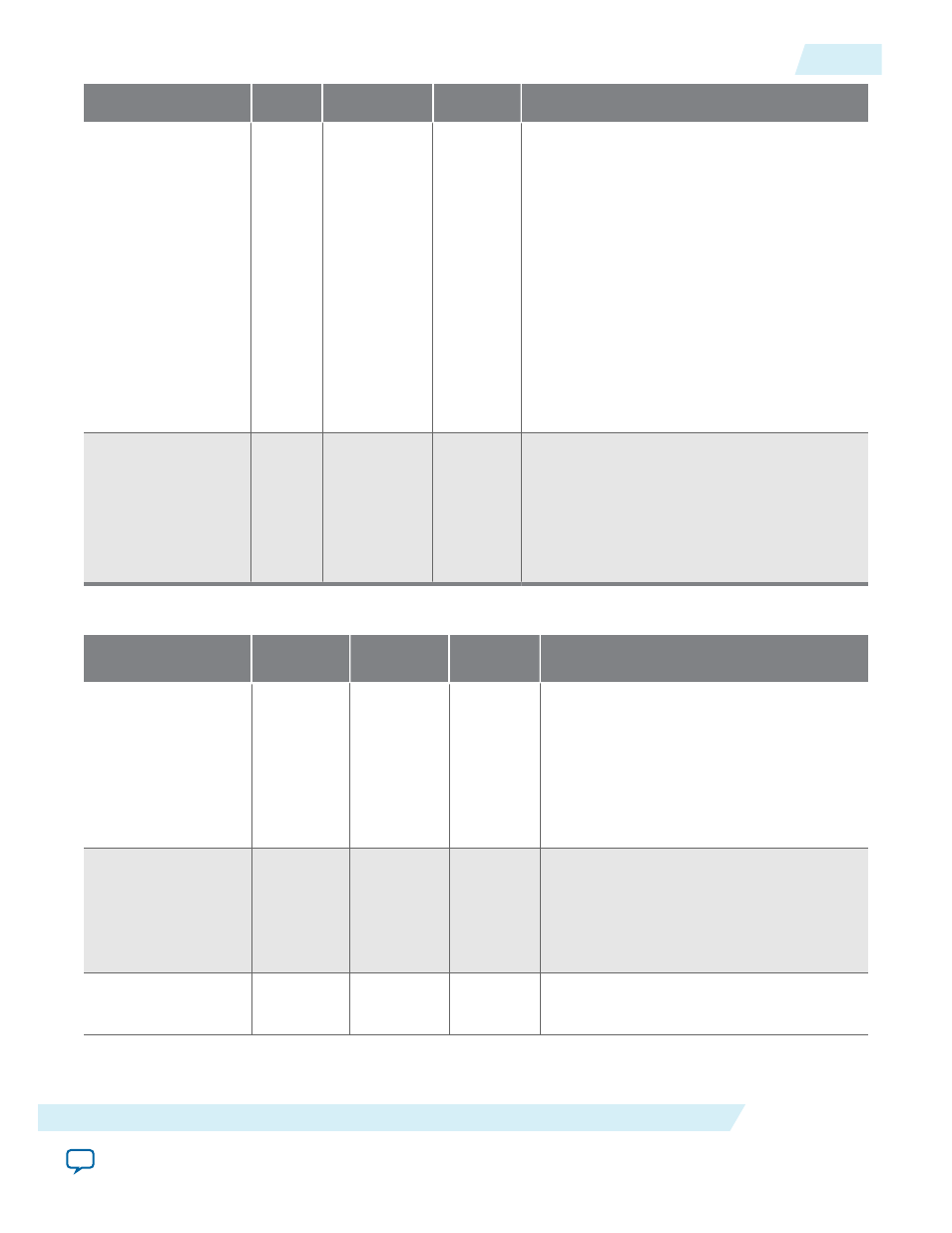

Signal

Width

Clock Domain

Direction

Description

error_rx

N+5

Standard

clocking:

user_clock

Advanced

clocking:

core_clock

Output

This vector indicates the state of the sink

adaptation module’s FIFO buffer. N

represents the number of lanes:

• [N+4]: An SEU error occurred and could

not be corrected (ECC enabled); Don't

care (ECC disabled)

• [N+3]: An SEU error occurred and was

corrected (ECC enabled); Don't care (ECC

disabled)

• [N+2]: FIFO buffer overflow

• [N+1]: FIFO buffer underflow

• [N]: Loss of alignment

• [N-1:0]: RX CRC 32 error

crc_error_

inject

1

Standard

clocking:

user_clock_tx

Advanced

clocking:

core_clock_tx

Input

This signal is used for CRC-32 error

injection.

Table 4-9: Interlaken PHY IP Core Signals and Native PHY IP Core Signals (Interlaken Mode)

Signal

Width

Clock

Domain

Direction

Description

phy_mgmt_clk

1

N.A.

Input

Clock input for the Avalon-MM PHY

management interface within the

Interlaken PHY IP core or Native PHY IP

core. This signal also clocks the transceiver

reconfiguration interface and sequences

the reset state machine in the clock

generation logic.

phy_mgmt_clk_

reset

1

phy_mgmt_

clk

Input

Global reset signal that resets the entire IP

including MAC, fPLL (available in

standard clocking mode), and Interlaken

PHY IP core or Native PHY IP core. This

signal is active high and level sensitive.

phy_mgmt_

addr[8:0]

9

phy_mgmt_

clk

Input

Control and status register (CSR) address

for Stratix V and Arria V GZ devices.

UG-01126

2015.05.04

Signals

4-29

SerialLite III Streaming IP Core Functional Description

Altera Corporation