Altera Avalon Verification IP Suite User Manual

Page 66

Chapter 5: Avalon-MM Monitor

5–3

Parameters

May 2011

Altera Corporation

Avalon Verification IP Suite User Guide

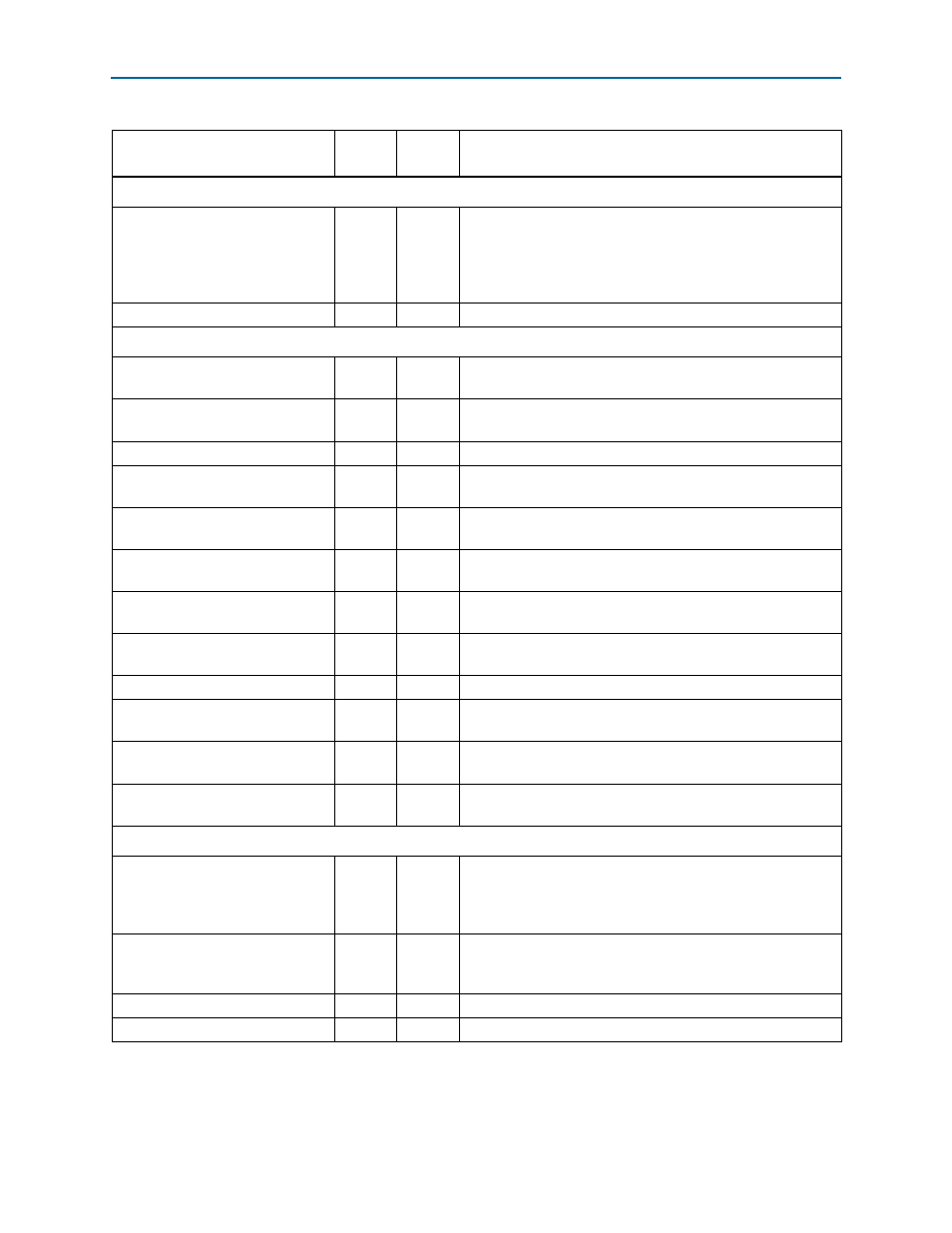

Burst Attributes

Linewrap burst

On

On/Off

When On, the address for bursts wraps instead of an

incrementing. With a wrapping burst, when the address reaches

a burst boundary, it wraps back to the previous burst boundary

such that only the low order bits need to be used for

addressing.

Burst on burst boundaries only

On

On/Off

When On, memory bursts are aligned to the address size.

Miscellaneous

Read response timeout (cycles)

100

—

Specifies when a timeout occurs if

readdatavalid

is not

asserted.

Avalon write timeout (cycles)

100

—

Specifies when a timeout occurs if a burst write transfer has not

completed.

Waitrequest timeout (cycles)

1024

—

Timeout period for the continuous assertion of

waitrequest

.

Maximum pending reads

1

—

Specifies the maximum number of pipelined reads that can be

pending.

Fixed read latency (cycles)

0

—

Sets the read latency for fixed-latency slaves. Not used on

interfaces that include the

readdatavalid

signal.

Maximum read latency (cycles)

100

—

Specifies the maximum read latency in cycle for test coverage

function

Maximum waitrequest read cycles

(for coverage)

100

—

Specifies the maximum wait time allowed for read cycle for

coverage.

Maximum waitrequest write cycles

(for coverage)

100

—

Maximum wait time allowed for write cycle for coverage.

Maximum continuous read (cycles)

5

—

Maximum continuous read time allowed for coverage.

Maximum continuous write

(cycles)

5

—

Maximum continuous write time allowed for coverage.

Maximum continuous waitrequest

(cycles)

5

—

Maximum continuous wait request time allowed for coverage.

Maximum continuous

readdatavalid (cycles)

5

—

Maximum continuous readdatavalid time allowed for coverage.

Timing

Fixed read wait time (cycles)

1

—

For master interfaces that do not use the

waitrequest

signal,

the read wait time indicates the number of cycles before the

master responds to a read. The timing is as if the master

asserted

waitrequest

for this number of cycles.

Fixed write wait time (cycles)

0

—

For master interfaces that do not use the

waitrequest

signal,

the write wait time indicates the number of cycles before the

master accepts a write.

Registered waitrequest

Off

On/Off

Specifies whether to turn on the register stage.

Registered Incoming Signals

Off

On/Off

Specifies whether to register incoming signals.

Table 5–1. Parameters for the Avalon-MM Monitor (Part 2 of 2)

Parameter

Default

Value

Legal

Values

Description