Generating a qsys testbench system, Generating a qsys testbench system –3 – Altera Avalon Verification IP Suite User Manual

Page 170

Chapter 2: Qsys Tutorial

2–3

Verifying Avalon-ST DUT

May 2011

Altera Corporation

Avalon Verification IP Suite User Guide

6. In the parameter editor, change the parameter values to match the values listed in

7. Click Finish.

8. Right-click on the

sc_fifo_0

component and select Rename. Rename the

component to “dut”

.

9. On the System Contents tab, in the Export column, rename the exported interface

names to match the names listed in

.

Generating a Qsys Testbench System

To generate a testbench system for the DUT, follow these steps:

1. On the Generation tab, change the parameter values to match the values listed in

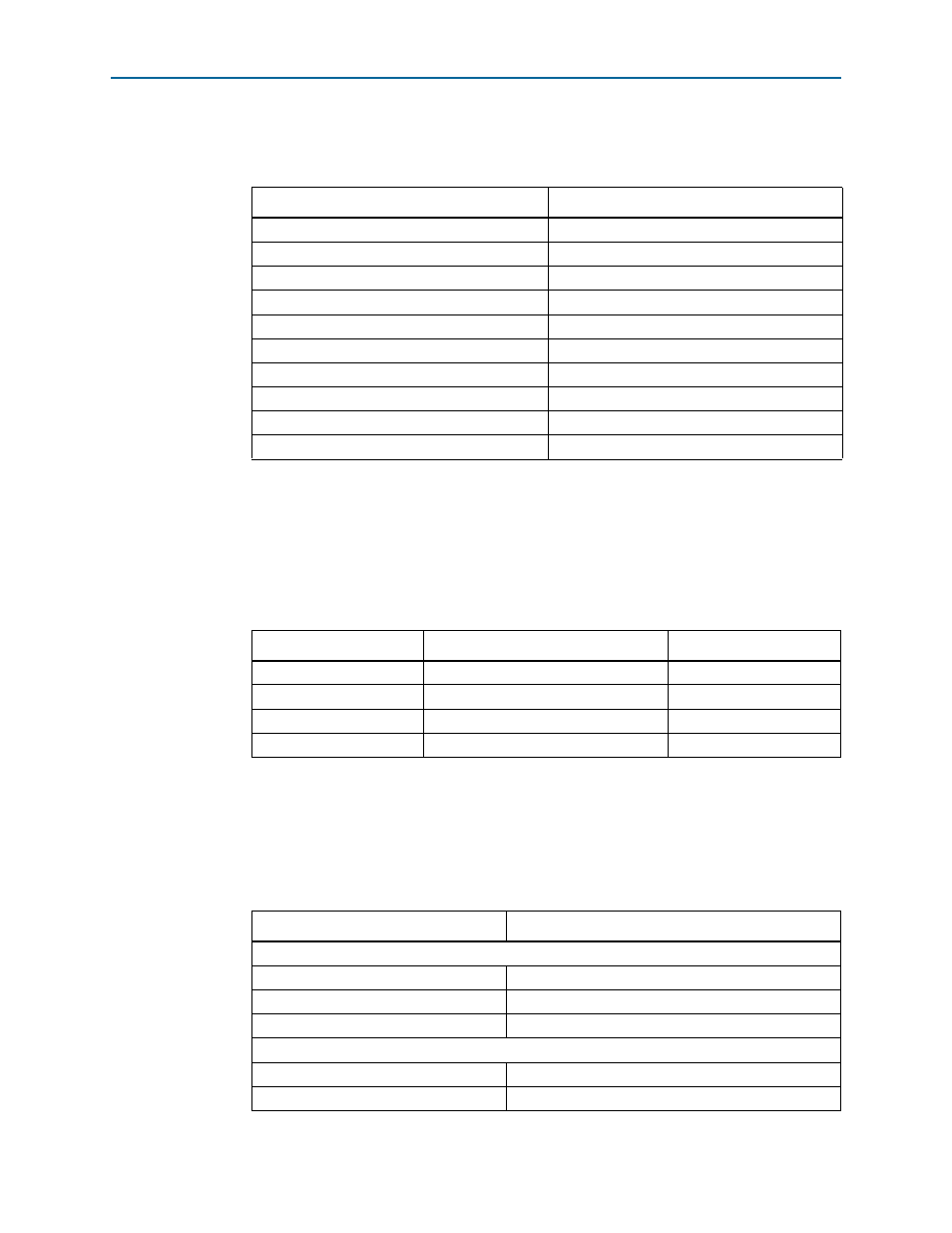

Table 2–1. Avalon-ST Single Clock FIFO Parameter Values

Parameters

Value

Symbols per beat

4

Bits per symbol

8

FIFO depth

2

Channel width

3

Error width

3

Use packets

On

Use fill level

Off

Use store and forward

Off

Use almost full status

Off

Use almost empty status

Off

Table 2–2. Avalon-ST Single Clock FIFO Exported Interface Names

Interface Name

Description

Export Name

clk

Clock Input

clk

clk_reset

Reset Input

reset

in

Avalon Streaming Sink

st_in

out

Avalon Streaming Source

st_out

Table 2–3. Generation Tab Parameter Values

Parameters

Value

Simulation

Create simulation model

None

Create testbench Qsys system

Standard, BFMs for standard Avalon Interfaces

Create testbench simulation model

Verilog

Synthesis

Create HDL design files for synthesis

Turned off

Create block symbol file (.bsf)

Turned off