Altera Avalon Verification IP Suite User Manual

Page 160

1–4

Chapter 1: SOPC Builder Tutorial

Verifying Avalon-MM Slave DUT

Avalon Verification IP Suite User Guide

May 2011

Altera Corporation

6. Click Finish.

7. Right-click on the component and select Rename. Rename the component name to

“master_bfm”.

8. In the search field located in the Component Library panel, type “onchip

memory”. From the search results, double-click the On-Chip Memory (RAM or

ROM)

component.

9. Retain the default settings for the on-chip RAM, and click Finish.

10. Right-click on the RAM and click Rename. Rename the component name to

“ram”.

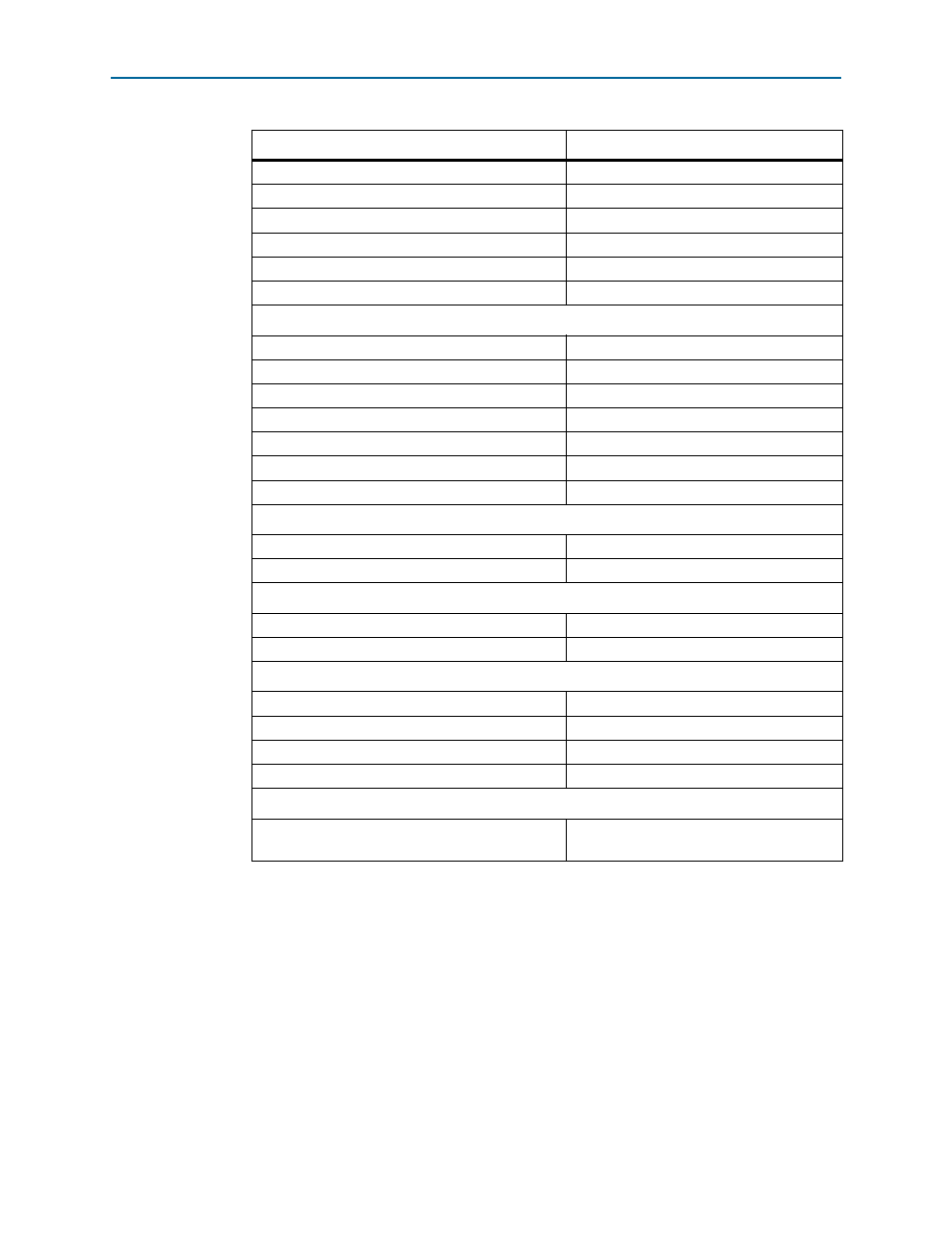

Use the debugaccess signal

Off

Use the waitrequest signal

On

Use the transactionid signal

Off

Use the write response signals

Off

Use the read response signals

Off

Use the clken signals

Off

Port Polarity

Assert reset high

On

Assert waitrequest high

On

Assert read high

On

Assert write high

On

Assert byteenable high

On

Assert readdatavalid high

On

Assert arbiterlock high

Off

Burst Attributes

Linewrap burst

Off

Burst on burst boundaries only

Off

Miscellaneous

Maximum pending reads

1

Fixed read latency (cycles)

0

Timing

Fixed read wait time (cycles)

0

Fixed write wait time (cycles)

0

Registered waitrequest

Off

Registered Incoming Signals

Off

Interface Address Type

Set master interface address type to symbols or

words

SYMBOLS

Table 1–1. Master BFM Parameter Values (Part 2 of 2)

Parameter

Value